# Reduce EMI and Improve Power Delivery with Embedded Capacitance

WHEN ENHANCED PERFORMANCE IS REQUIRED

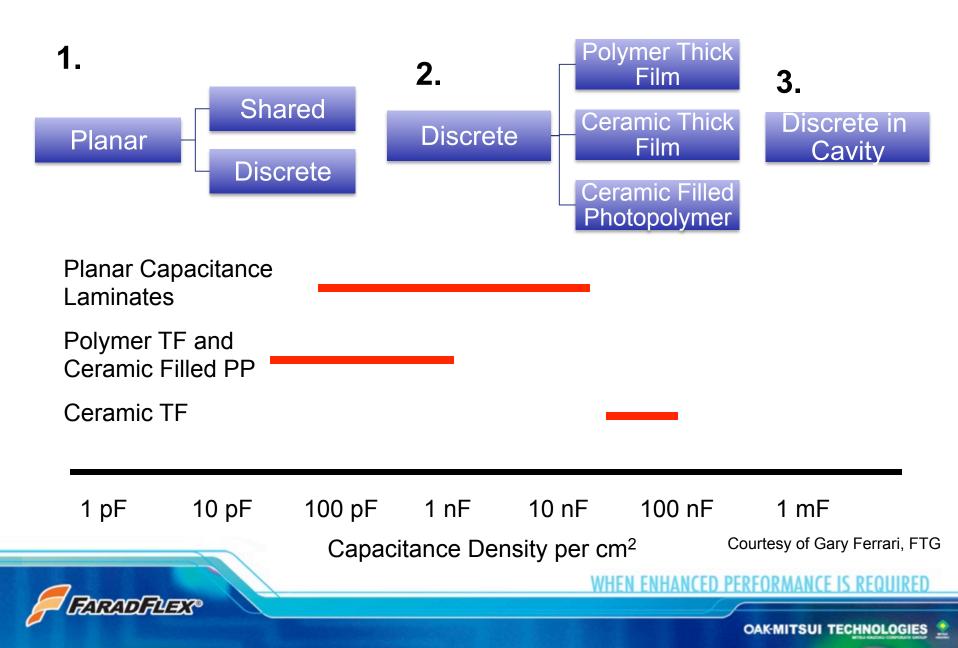

### Types of **EMBEDDED** capacitance

### Types of **EMBEDDED** capacitance

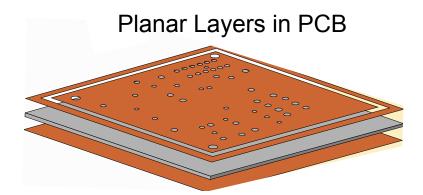

Use this is an existing stack up of layers in the PCB

#### Plus

- Easy

- Addresses many issues with PCB design and power delivery

- Same or lower cost

- More reliable

#### Minus

- Limited capacitance currently available

Discrete in PCB cavity

Leave a cavity open in the PCB and then place the capacitor and solder in place and then fill the cavity

#### Plus

- Full values of capacitance available

#### Minus

- Manufacturing and design difficult

- Costly

- Less reliable

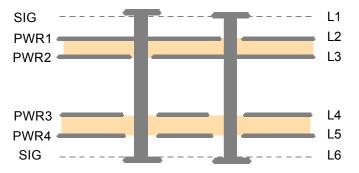

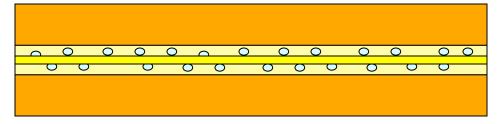

#### What is a Planar Capacitor?

Conductive plane pair with dielectric separation:

The current planar ultra-thin material sets:

- 1. Polymer film such as polyimide (**Dupont**)

- 2. Polymer film and resin combination (**Dupont and Oak-Mitsui**)

- Unsupported resin filled with higk Dk or other types of particles (**3M and Oak-Mitsui**)

# F FARAD FLEX

2014 Survey by IPC

- 1. Of the companies in the survey 30% of their PCB's are using Embedded Capacitance

- 2. In 2015 and beyond the expectation are that this will more than double

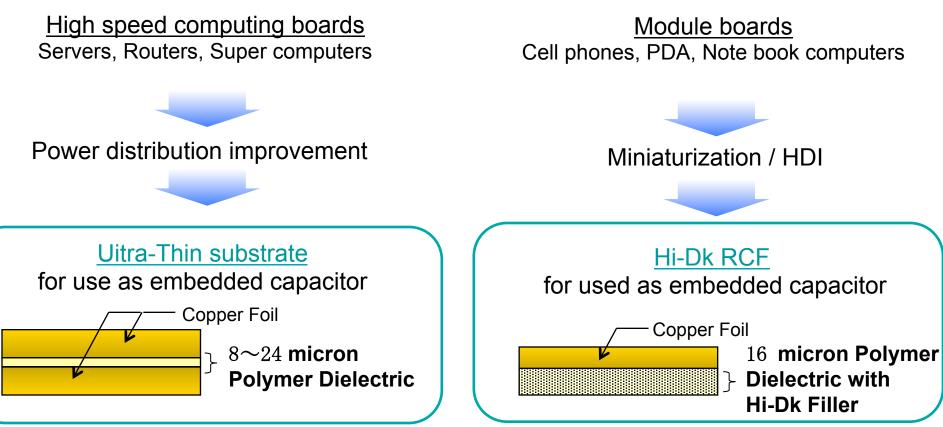

Why Embedded Capacitance and Why Thin Dielectrics?

- Better PDN

- Lower profile

- More design space

- Low inductance

- Low impedance

- Reduced noise

- Space...

- Thickness

reduction...

- Weight reduction

- Higher reliability

- In some designs better thermal transfer

- Etc.

#### Solution

HEN ENHANCED PERFORMANCE IS REQUIRED

Expectation by using thin planar capacitance material

- Improved electrical performance

- Reduce system cost

- Reduce board thickness

- Reduce prototype revisions

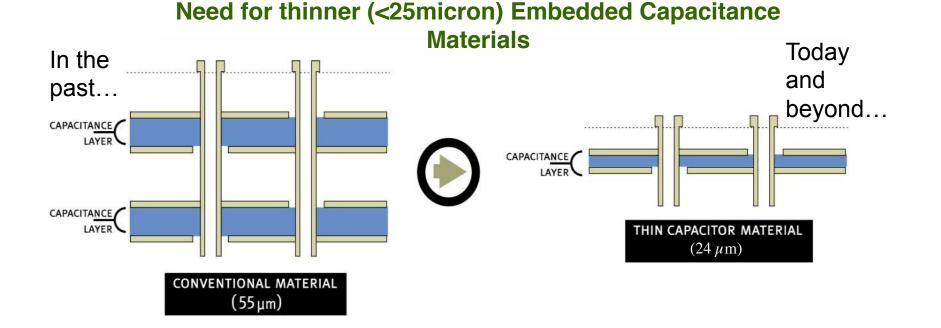

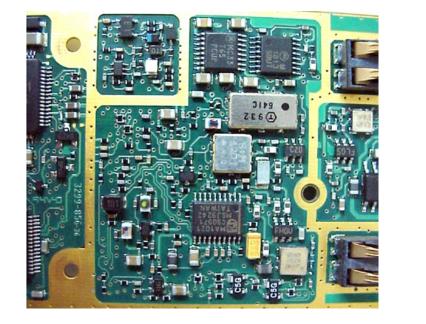

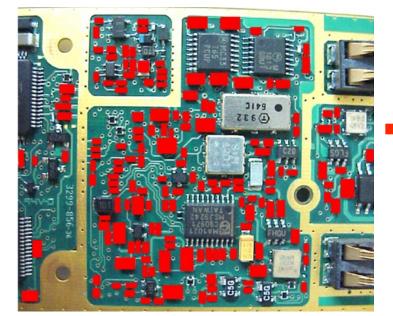

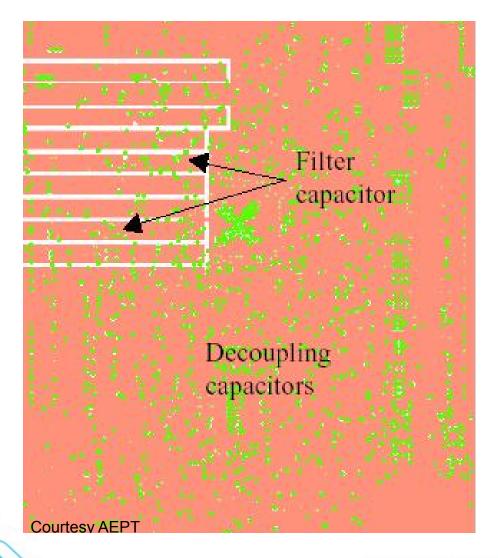

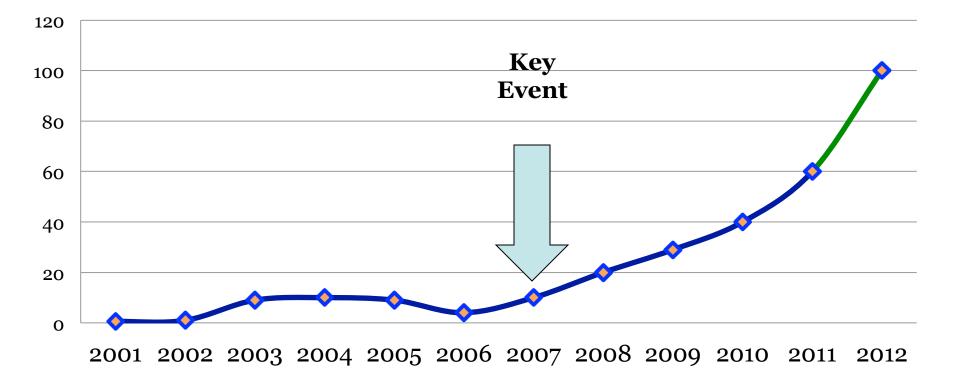

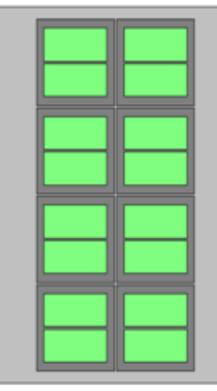

### Component density is reaching its limit

Source: Richard Ulrich University of Arkansas

High capacitance and capacitance uniformity are key

WHEN ENHANCED PERFORMANCE IS REQUIRED

Passive

components

### 8 Layer HDI Design

With shared planar embedded capacitance

Courtesy of Gary Ferrari, FTG

### 14 Layer Design

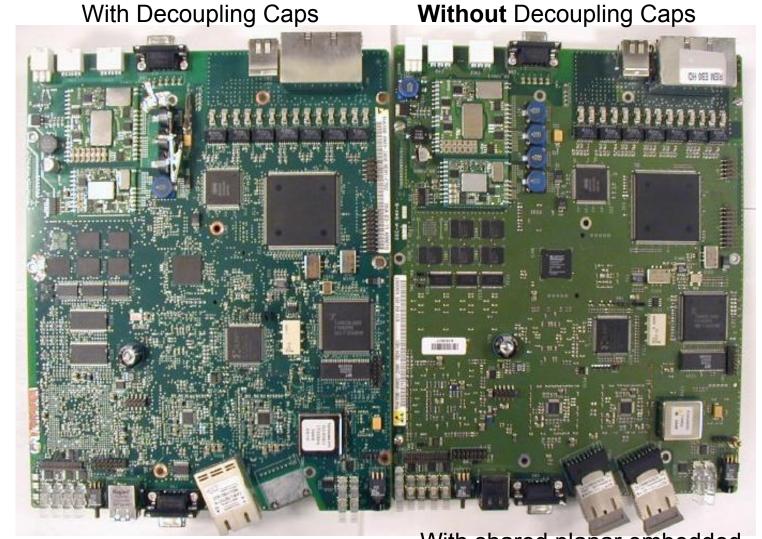

#### With Decoupling Caps

#### Without Decoupling Caps

Courtesy of Gary Ferrari, FTG

With shared planar embedded capacitance

Discrete Capacitors designed into a Distributed Capacitor Plane

FARADFLEX

Courtesy of Gary Ferrari, FTG

WHEN ENHANCED PERFORMANCE IS REQUIRED

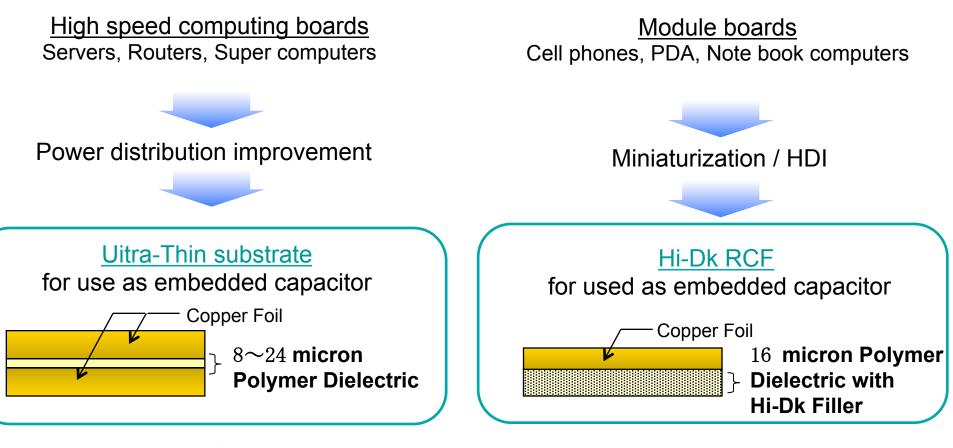

### Two Approaches to Embedded Capacitance

#### Solution

VHEN ENHANCED PERFORMANCE IS REQUIRED

#### WHEN ENHANCED PERFORMANCE IS REQUIRED

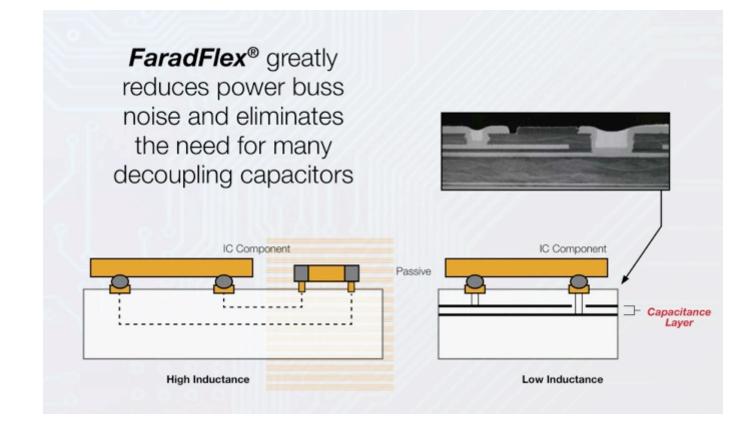

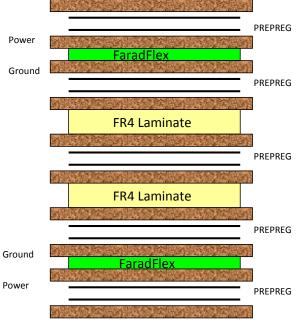

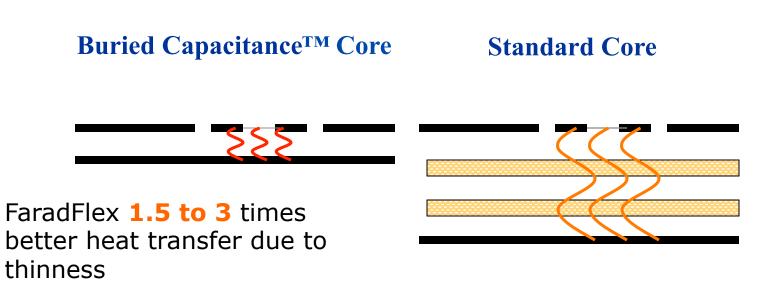

#### FaradFlex® compared to traditional material

- *FaradFlex*<sup>®</sup> is 1/2 to 1/6 the thickness compared to the typical "thinnest" laminate using glass cloth reinforcement.

- *FaradFlex*<sup>®</sup> increases thermal transfer from the PCB due to the ultra thin power-ground substrate.

- Dielectic withstanding voltage is typically 10 times better with *FaradFlex*<sup>®</sup> than the traditional FR-4 laminates and similar materials.

ARADFLEX

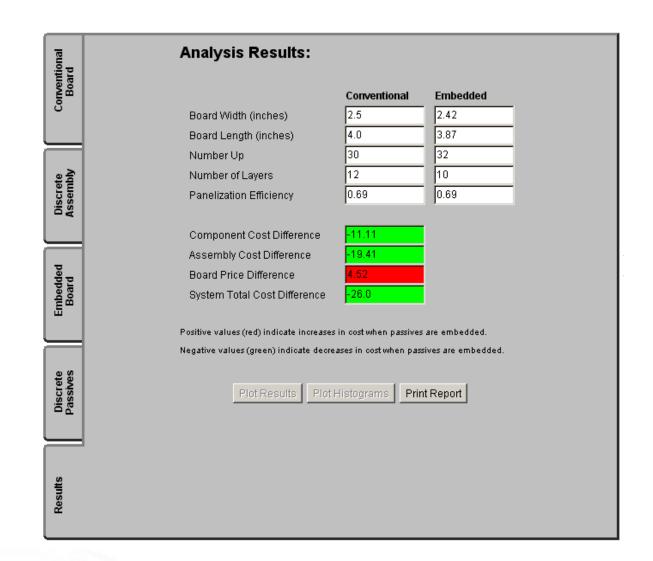

### **Background / Motivation**

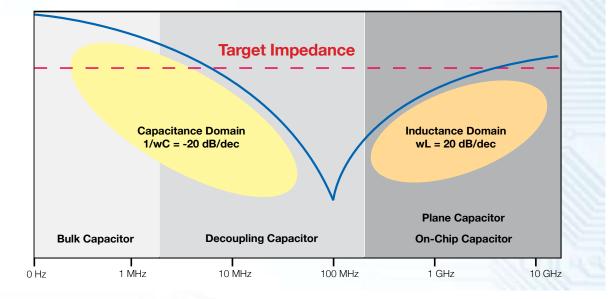

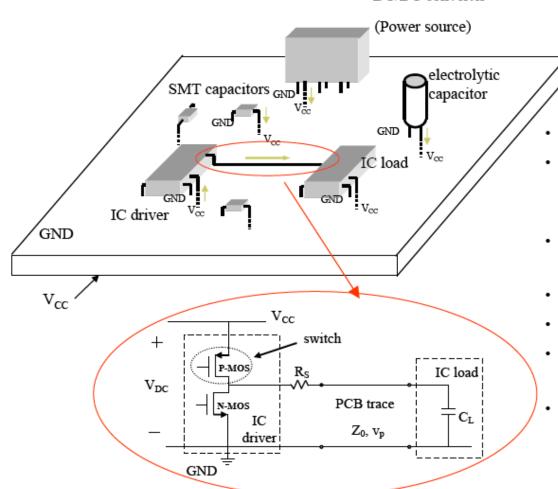

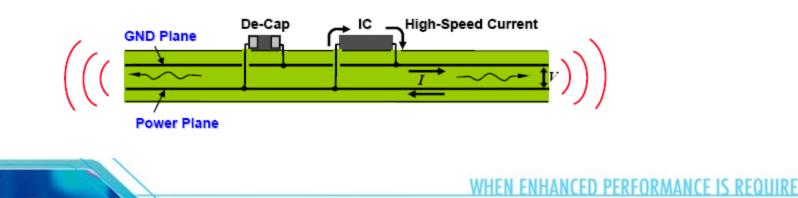

### **TYPICAL/ TRADITIONAL POWER DISTRIBUTION NETWORK**

Courtesy of Dr. Jun Fan

ARADFLEX

DC/DC converter

- Capacitor interconnects;

- Individual capacitor values and packaging forms;

- Number of capacitors needed;

- Capacitor placement;

- PCB stack-up;

- Power/ground plane pair geometry;

- Segmentation and isolation

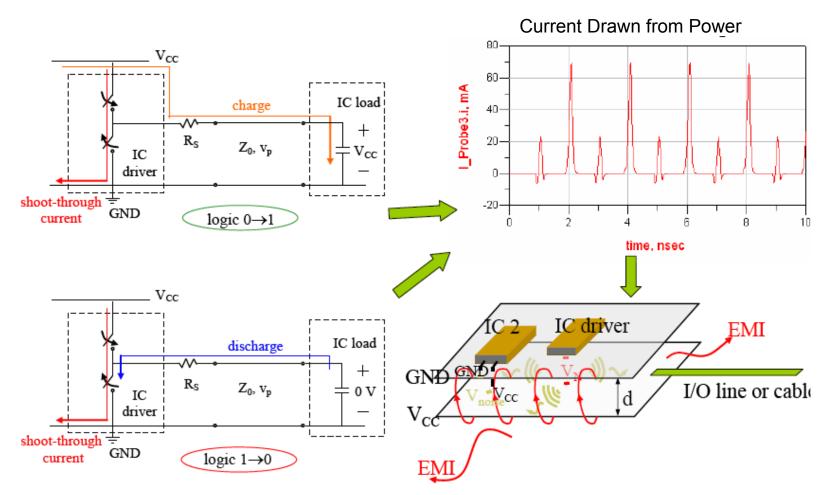

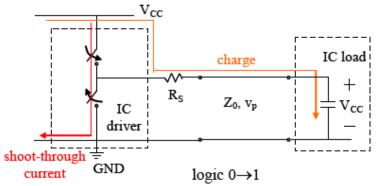

# Device Switching And Noise Current

J. L Knighten, B. Archambeault, J. Fan, et. al., "PDN Design Strategies: IV. Sources of PDN Noise," *IEEE EMC Society Newsletter*, Winter 2007, Issue No. 212, pp. 66-76.

WHEN ENHANCED PERFORMANCE IS REQUIRED

# PDN Design Objectives

- 1. Ensure charge supply for logic transitions

- Enough capacitance to store charge

- Enough charge readily available for short transitions

- 2. Minimize noise voltage distribution on the  $V_{CC}$ /GND plane pair

- Low power bus impedance over frequency

- Noise decoupling

- Noise isolation

cy oling GND GND GND C V d I/O line or cable on V<sub>CC</sub> K<sup>N</sup> d I/O line or cable

OAK-MITSUI TECHNOLOGIES

FD PERFORMANCE IS REQUIRE

# STANDARD Dk PRODUCT

| Properties                                          | Test<br>Method         | MC24M          | MC12M          | MC8M           | MC25L          |

|-----------------------------------------------------|------------------------|----------------|----------------|----------------|----------------|

| Dielectric Thickness, µm                            | IPC or<br>others       | 22             | 12             | 12 8           |                |

| Cp @1 MHz, nF/in <sup>2</sup> (pF/cm <sup>2</sup> ) | Nominal                | 1.2 (180)      | 1.9 (300)      | 3.1 (480)      | 1.0 (130)      |

| Dk (Dielectric Constant)<br>@ 1 MHz/ 1 GHz          | IPC TM-<br>650 2.5.5.2 | 4.4/ 3.5       | 4.4/ 3.5       | 4.4/ 3.5       | 3.9/ 3.8       |

| Df (Loss Tangent)<br>@1 MHz/ 1 GHz                  | IPC TM-<br>650 2.5.5.2 | 0.015/ 0.016   | 0.015/ 0.020   | 0.016/ 0.021   | 0.004/ 0.005   |

| Peel Strength, lbs/ linear in.                      | IPC TM-<br>650 2.5.5.2 | 8              | 8              | 5              | 8              |

| Dielectric Strength, kV/mil                         | IPC TM-<br>650 2.4.9   | >7             | >7             | >5             | >7             |

| Tensile Strength, MPa (kpsi)                        | ASTM<br>D-882A         | 219 (31.8)     | 194 (28.2)     | 126 (18.3)     | 227 (32.9)     |

| Elongation, %                                       | ASTM<br>D-882A         | 36.0           | 13.5           | 8.5            | 47.0           |

| CTE, ppm/°C,<br>x-y (40-200°C), TMA                 | ТМА                    | 24             | 23             | 32             | 30             |

| Dielectric Withstanding Voltage (Hi-<br>Pot test)   | IPC TM-<br>650 2.5.7.2 | PASS<br>(500V) | PASS<br>(500V) | PASS<br>(500V) | PASS<br>(500V) |

| Thermal Stress (20Sec Float<br>@288C), Times        | -                      | >10            | >10            | >10            | >10            |

| THB, 85°C/85%RH/ dc bias                            | 1000hr                 | PASS           | PASS           | PASS           | PASS           |

| Flammability/Temp Rating                            | UL                     | V0<br>130°C    | V0<br>130°C    | V0<br>125°C    | V0<br>130°C    |

| PWB Processing                                      | -                      | Both sides     | Both sides     | Both sides     | Both sides     |

Note: This chart provides the typical values for FaradFlex product.

# HIGH Dk PRODUCT

| Properties                                          | Test<br>Method         | MC12TM          | МС8ТМ           | MC16T            | MC25ST           | MC25LD            |

|-----------------------------------------------------|------------------------|-----------------|-----------------|------------------|------------------|-------------------|

| Dielectric Thickness, µm                            | IPC or<br>others       | 12              | 8               | 16               | 25               | 25                |

| Cp @1 MHz, nF/in <sup>2</sup> (pF/cm <sup>2</sup> ) | Nominal                | 4.2 (650)       | 7.1 (1100)      | 11 (1700)        | 4.3 (660)        | 2.1 (320)         |

| Dk (Dielectric Constant)<br>@ 1 MHz/ 1 GHz          | IPC TM-<br>650 2.5.5.2 | 10.0/ 9.5       | 10.5/ 10.0      | 30.0/ 25,0       | 18.5/ 18.0       | 8.3/ 7.8          |

| Df (Loss Tangent)<br>@ 1 MHz/ 1 GHz                 | IPC TM-<br>650 2.5.5.2 | 0.015/<br>0.020 | 0.020/<br>0.021 | 0.034/<br>0.036  | 0.004/<br>0.008  | 0.0027/<br>0.0032 |

| Peel Strength, lbs/ linear in.                      | IPC TM-<br>650 2.5.5.2 | 5               | 5               | 5                | 4                | 4                 |

| Dielectric Strength, kV/mil                         | IPC TM-<br>650 2.4.9   | 5               | 4               | 2                | 2                | 2                 |

| Tensile Strength, MPa (kpsi)                        | ASTM<br>D-882A         | 153 (22.2)      | 127 (18.4)      | NA               | NA               | NA                |

| Elongation, %                                       | ASTM<br>D-882A         | 31.4            | 14.0            | NA               | NA               | NA                |

| CTE, ppm/°C,<br>x-y (40-200°C), TMA                 | ТМА                    | 28              | 22              | 17(α1)<br>42(α2) | 32(α1)<br>97(α2) | 55                |

| Dielectric Withstanding Voltage<br>(Hi-Pot test)    | IPC TM-<br>650 2.5.7.2 | PASS<br>(500∨)  | PASS<br>(250V)  | PASS<br>(100V)   | PASS<br>(100V)   | PASS<br>(100V)    |

| Thermal Stress (20 Sec Float<br>@288C), Times       | -                      | >10             | >10             | >10              | >10              | >10               |

| THB, 85°C/85%RH/ dc bias                            | 1000hr                 | PASS            | PASS            | PASS             | PASS             | PASS              |

| Flammability/Temp Rating                            | UL                     | V0<br>130°C     | V0<br>130 °C    | V0<br>130°C      | Pending          | Pending           |

| PWB Processing                                      | -                      | Both sides      | Both sides      | Sequential       | Sequential       | Sequential        |

Note: This chart provides the typical values for FaradFlex product.

# **Embedded Capacitance Materials**

**First Type of Embedded Capacitance Laminate**

- Copper

- Epoxy or other type resin bonded to a high performance polymer film

#### **Includes These:**

MC24M, MC12M, MC8M,

MC25L

CHARACTERISTICS

Most cost effective.

Best processabilty

Longest in history

Highest reliability

# **Embedded Capacitance Materials**

#### **Includes These:**

#### Second Type of Embedded Capacitance Laminate

Laminate constructed with:

- Copper

- **Unsupported epoxy resin** with barium titanate or other particles dispersed in the resin

MC16T, MC25ST, MC25LD

### CHARACTERISTICS

Most costly laminate Least processabilty Highest Dk, Highest capacitance Lowest reliability

# **Embedded Capacitance Materials**

#### Third Type of Embedded Capacitance Laminate

Laminate constructed with:

- Copper

- Supported epoxy resin and polymer film composite, barium titanate particles or other material dispersed

#### **Includes** These:

#### MC12TM, MC8TM

#### CHARACTERISTICS

Mid to more costly laminate High level of processabilty Very High Dk, Very High capacitance High reliability, High withstanding voltage

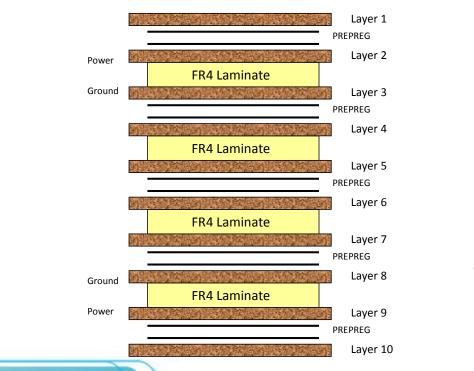

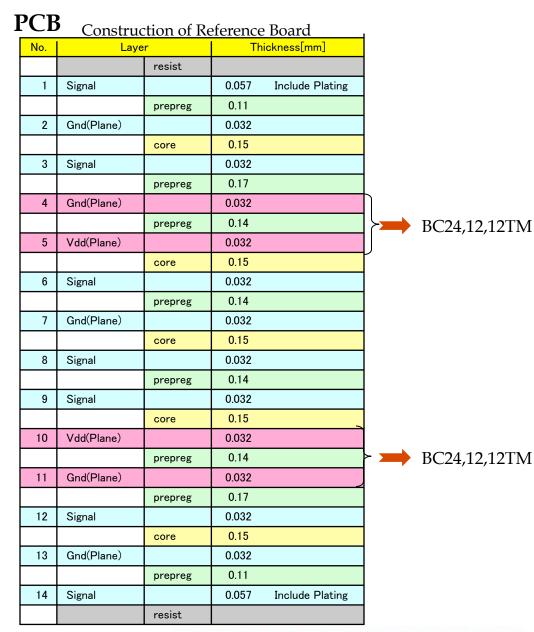

### **TYPICAL PCB DESIGN AND STACK UP**

WHEN ENHANCED PERFORMANCE IS REQUIRED

# Replace the Existing Power Ground Layer with FaradFlex

for use as power distribution layer

TARAD FLEX?

#### 10 LAYER PCB STACK-UP With 2 Power-Ground layers at L2/L3 and L8/L9 (using FaradFlex in the Power-Ground allows for buried capacitance)

With FR4 Power-Ground

With IMC24M Power-Ground

### Where to place FaradFlex?

MITSUI

### **IMPROVED IMPEDENCE/ INDUCTANCE**

WHEN ENHANCED PERFORMANCE IS REQUIRED

# **PCB Electrical Performance**

# **PCB Electrical Performance**

Discrete capacitors of 0.1µF have a resonance frequency of about 15 MHz Discrete capacitors of 0.01µF have a resonance frequency of about 40 MHz.

OAK-MITSUI TECHNOLOGIES

HANCED PERFORMANCE IS REQUIRED

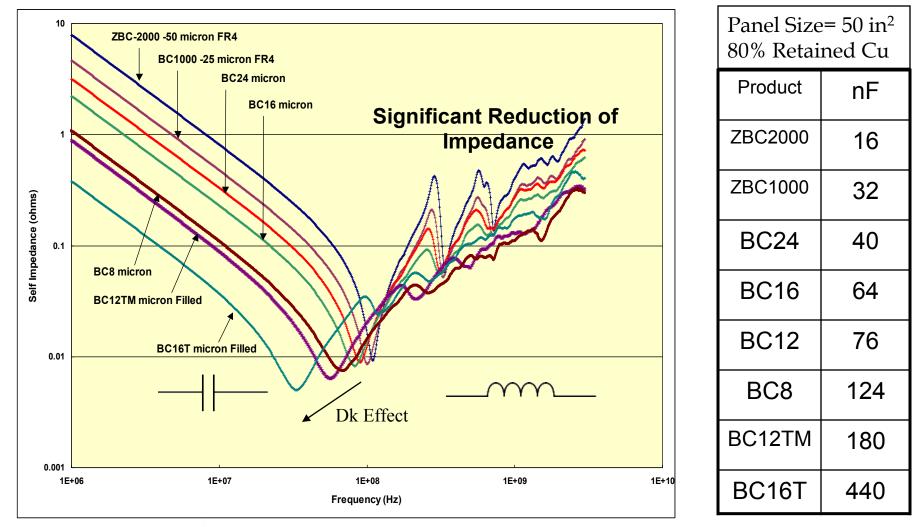

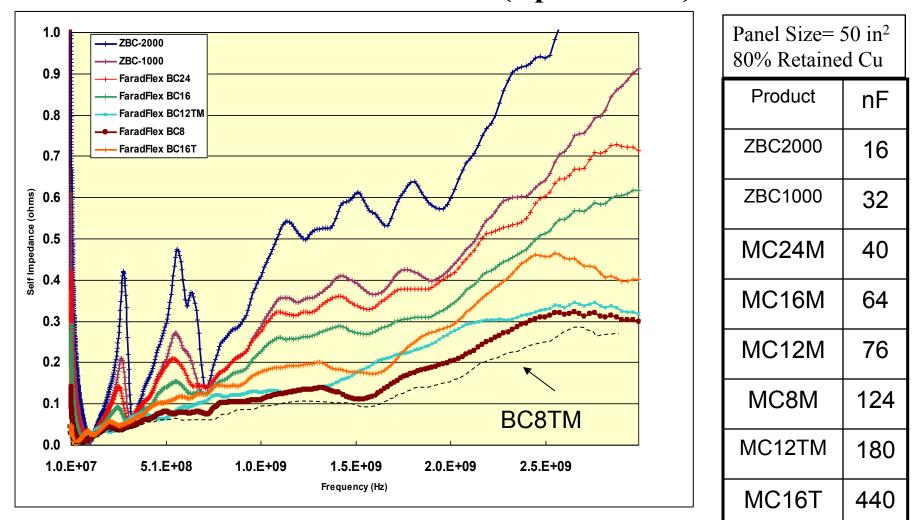

# PCB Electrical Performance (Up to 1 GHz)

ARADFUEX

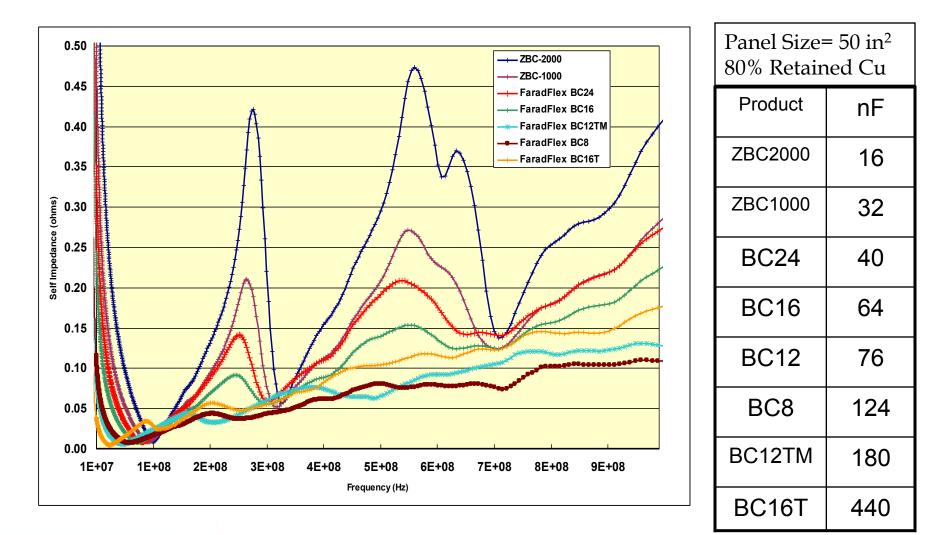

# PCB Electrical Performance (Up to 3 GHz)

ARADFLEX

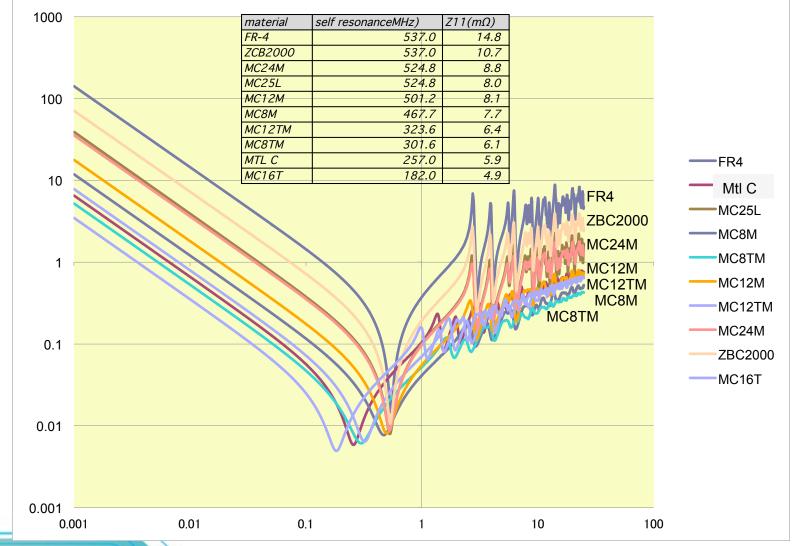

# **PCB Electrical Performance**

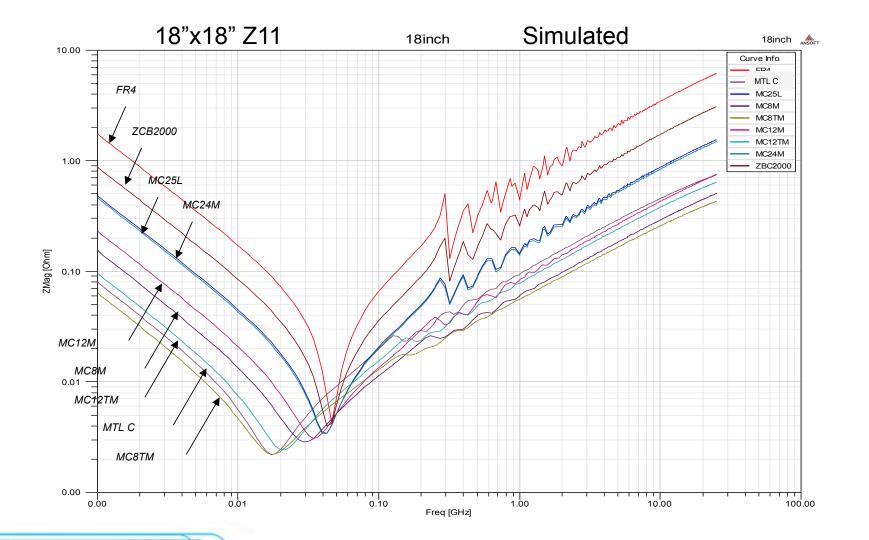

# **Studies Up to 25 GHz**

WHEN ENHANCED PERFORMANCE IS REQUIRED

### PCB Electrical Performance 2"x2" PCB Simulation (Data up to 25 GHz)

#### WHEN ENHANCED PERFORMANCE IS REQUIRED

# **PCB Electrical Performance**

### Data Up to 25 GHz)

FARADELESS

### RELIABILITY

WHEN ENHANCED PERFORMANCE IS REQUIRED

## **Reliability Tests**

FARADFLEX

| Description                                              |      |

|----------------------------------------------------------|------|

| 6x Through Hole Solder Shock                             | PASS |

| 6x Blind Via Solder Shock                                | PASS |

| Dielectric Thickness per Cross<br>Section within +/-10%  | PASS |

| T-288(>20min)                                            | PASS |

| IST Testing (500 cycles)                                 | PASS |

| Core Level Hi-Pot Testing<br>100Cores(100V/sec; 500Vmax) | PASS |

| Finished Circuit Level Hi-Pot                            |      |

| 50 circuits (100V/sec;<br>500Vmax)                       | PASS |

Courtesy of Sanmina-SCI

OAK-MITSUI TECHNOLOGIES

ANCE IS REQUIRE

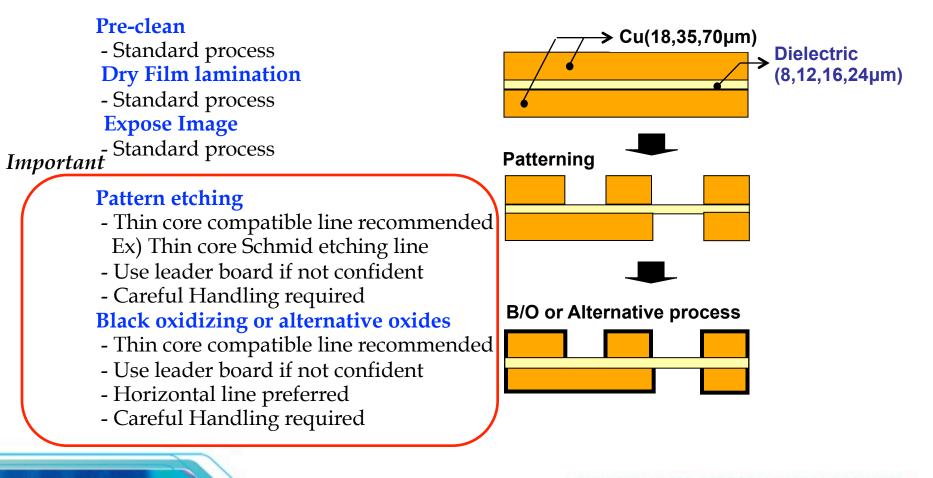

## PCB FABRICATION/ PROCESSING

WHEN ENHANCED PERFORMANCE IS REQUIRED

## **Processing guideline**

WHEN ENHANCED PERFORMANCE IS REQUIRE

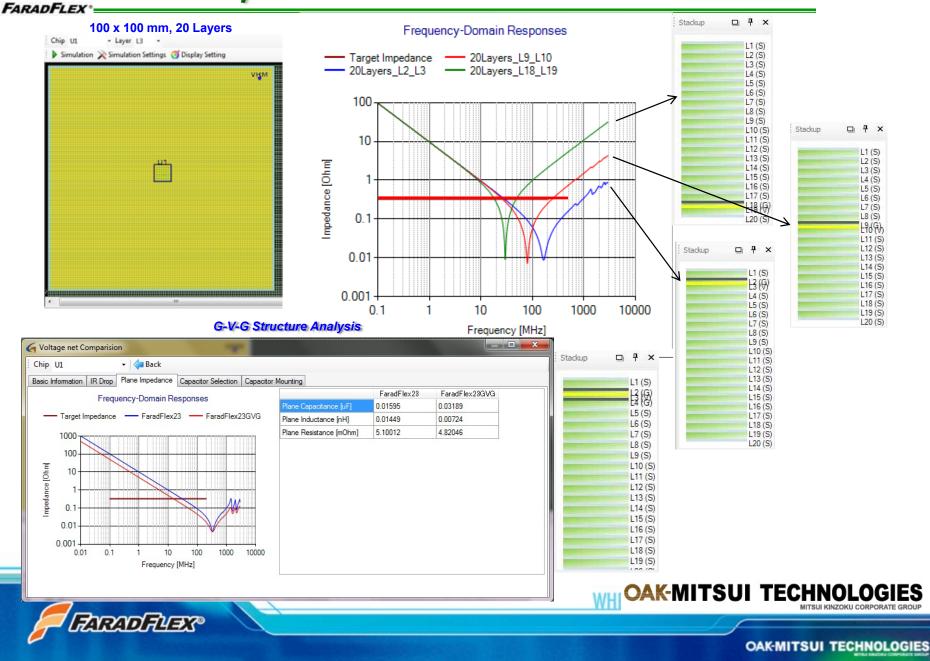

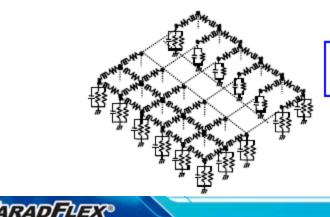

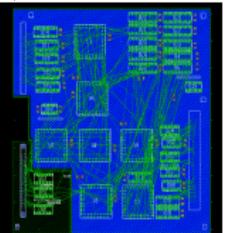

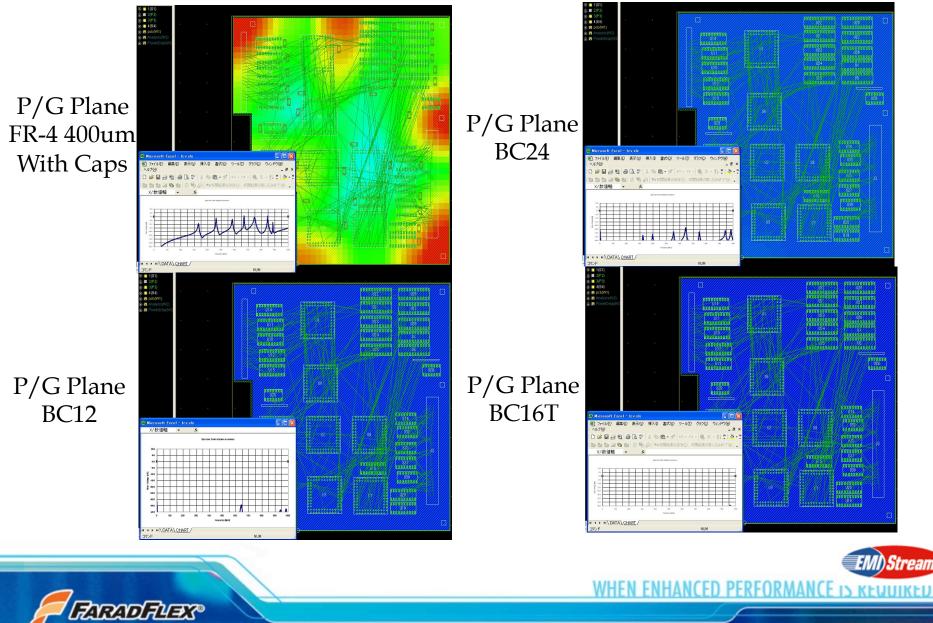

## **Power/Ground Plane Simulation**

- Utilize EMI Stream

- Developed by NEC

- Based on SPICE Model

- Input PCB Layout in Design Format (.dsn file)

- Output provide by standard design tools (Mentor Graphics, Cadence, etc.)

- Select thickness, Dk and Cu thickness of P/G planes

- Select frequency range

- Can add/subtract discrete SMT capacitors

## POWER DISTRIBUTIONS NETWORK SIMULATIONS RESONANCE/ NOISE/ EMI

WHEN ENHANCED PERFORMANCE IS REQUIRED

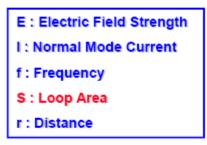

Why FaradFlex can reduce EMI?

- 1. Can minimize loop area  $(E_r = 1.316 \times 10^{-14} \times 1 \times f^2 \times S / r)$

- 2. Can minimize power bus noise

- 3. Can minimize resonance

- 4. Can minimize propagation to the edge (Related to Transfer Impedance (S21))

PI Simulation (EMIStream/PIStream)

- - Developed by NEC

- Based on PEEC method with Spice Simulation

- Input PCB Layout in Design File (xxx.dsn)

- Output provide by standard PCB layout tools (Mentor Graphics, Cadence, Zuken, etc.)

- Select thickness, Dk and Cu thickness of P/G planes

- Select frequency range

- Can add/remove discrete decoupling capacitors

INtimate Power Integr

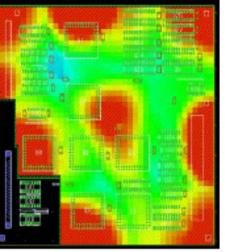

## **Resonance Distribution**

35- 0.1 μ F caps for power supply

#### 0.4mm (16 mil P/G)

Can not place caps!

35- 0.1 μ F caps for power supply

+44-0.1 μ F caps for resonances

24 μ m P/G Dk 4.4 No additional caps

0 d B

0 d B

Simulations provided by TechDream, Inc.

WHEN ENHANCED PERFORMANCE IS REQUIRED

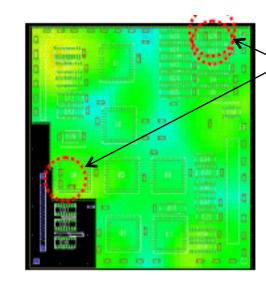

## **Resonance Distribution- Lower Noise Threshold** -26 d B -36 d B 12 $\mu$ m P/G 400 $\mu$ m (16 mil P/G) 24 $\mu$ m P/G Dk 10 79 caps Dk 4.4 35 caps 35 caps FARADFLEX

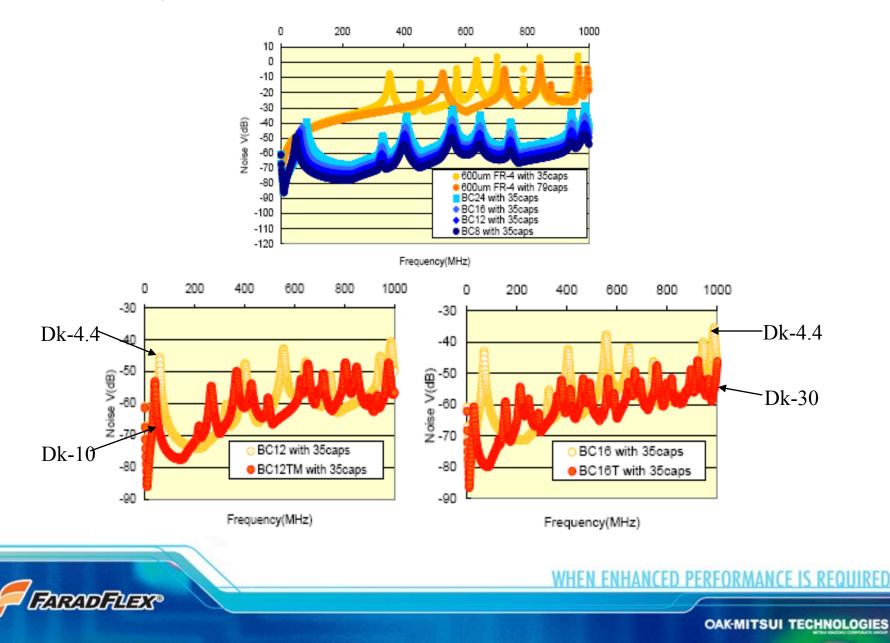

### **Frequency Response- Effect of Thickness, Dk**

### **Test Board- Simulation #2**

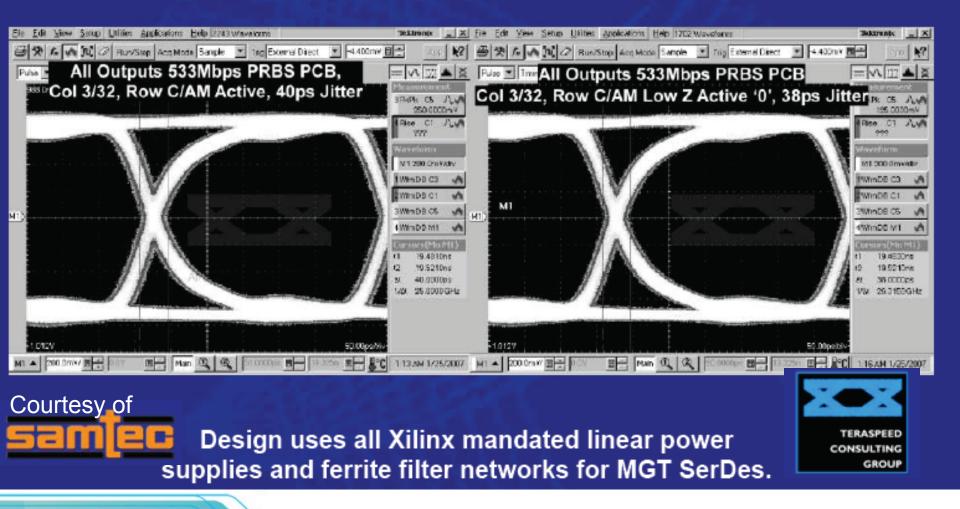

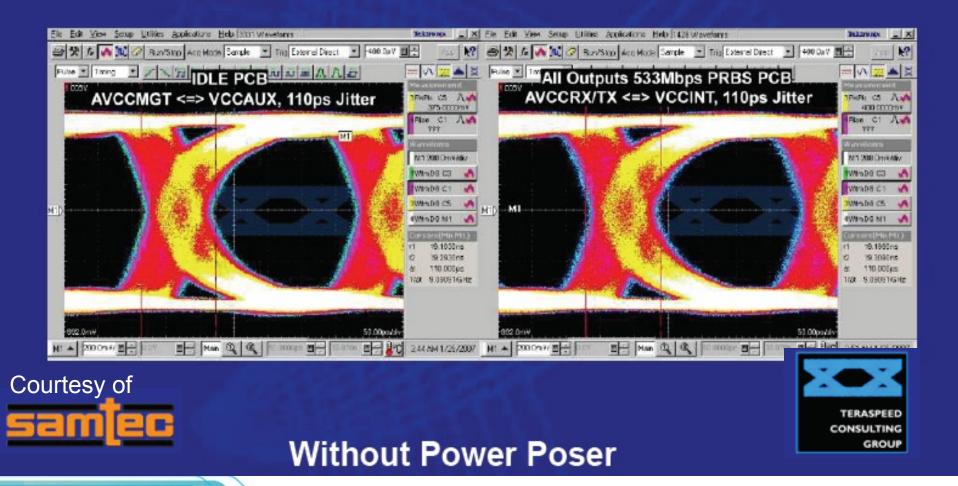

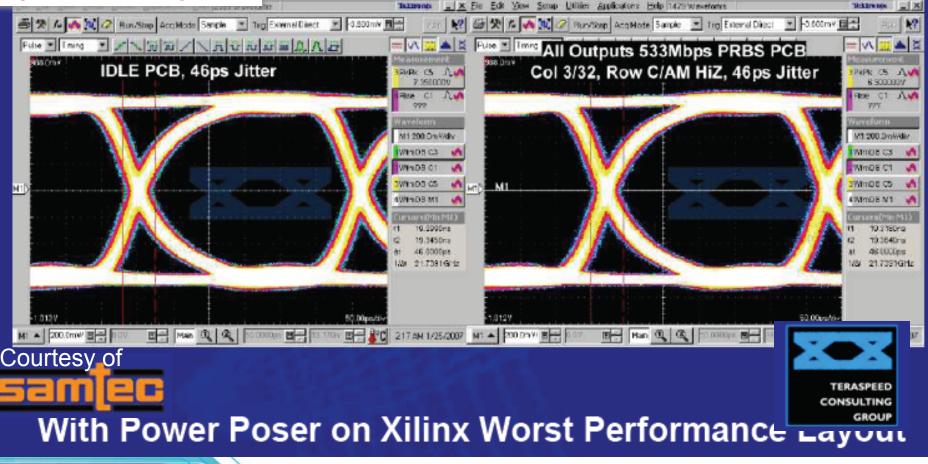

## ELECTRICAL BENEFITS Reduced Jitter/ Improved "Eye"

WHEN ENHANCED PERFORMANCE IS REQUIRED

#### WHEN ENHANCED PERFORMANCE IS REQUIRED

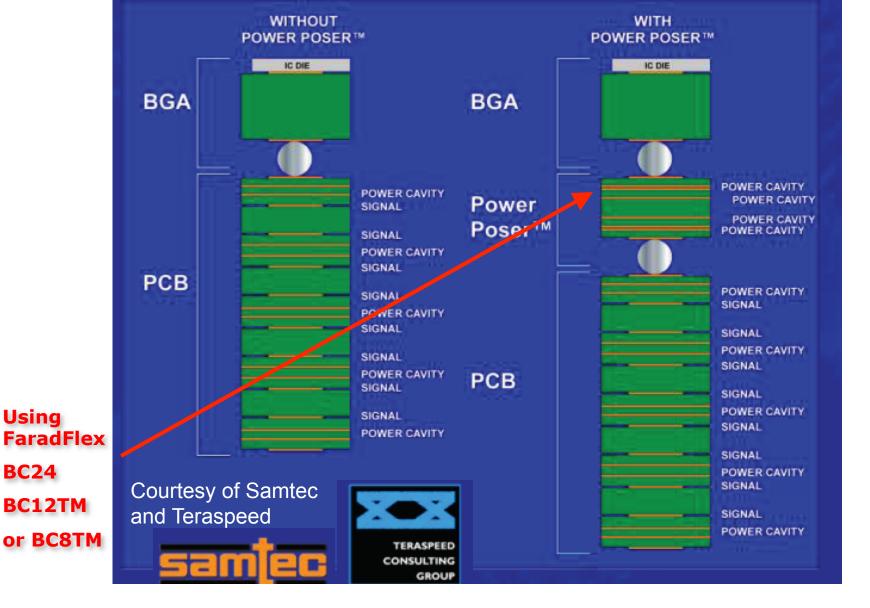

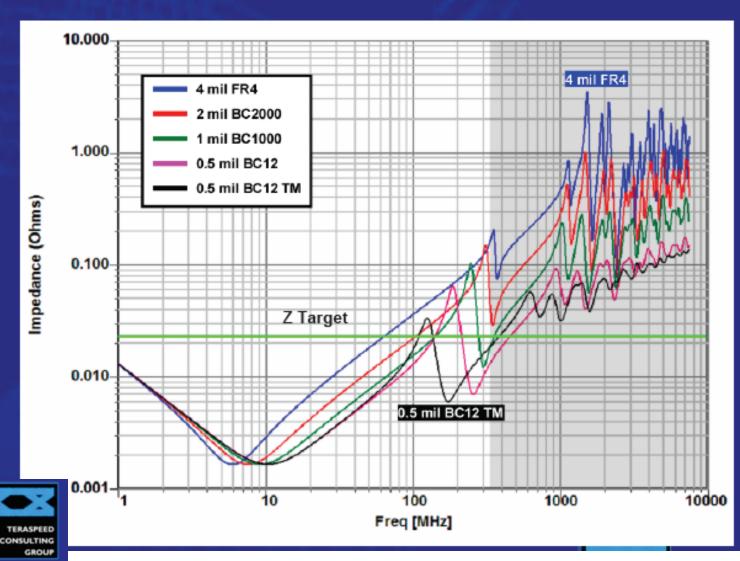

### 0402 Capacitors with 4 mil Deep Planes Various Plane Thicknesses on 6" x 6" PCB

Reduction in dielectric thickness decrease impedance, but also lowers resonance frequency.

Reduction in dielectric thickness increases magnitude of peaks.

Increase in material Er lowers resonance frequency.

Courtesy of Samtec and Teraspeed

ARADFLEX

#### WHEN ENHANCED PERFORMANCE IS REQUIRED

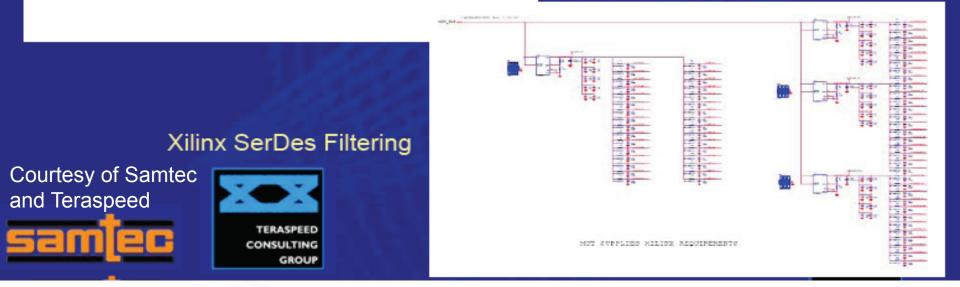

## **SerDes Filtering Comparison**

ARADFLEX

#### PowerPoser<sup>™</sup> SerDes Filtering

#### WHEN ENHANCED PERFORMANCE IS REQUIRED

## Xilinx Guidelines Board SerDes Best Performance @ 3.125 Gbps

WHEN ENHANCED PERFORMANCE IS REQUIRED

## Xilinx Filter Network with SMPS Performance @ 3.125 Gbps

ARADFLEX

WHEN ENHANCED PERFORMANCE IS REQUIRED

## PowerPoser™ DirectDrop™ Eval Board Measurements SerDes

#### Using FaradFlex BC12TM as the key layer in the Interposer

WHEN ENHANCED PERFORMANCE IS REQUIRED

## NEC CASE STUDY

WHEN ENHANCED PERFORMANCE IS REQUIRED

(by courtesy of NEC System Technology, Inc. & NEC Information Technology, Inc.)

FARADFLEX®

Total EN 2.368 ±0.2mm PERFORMANCE IS REQUIRED

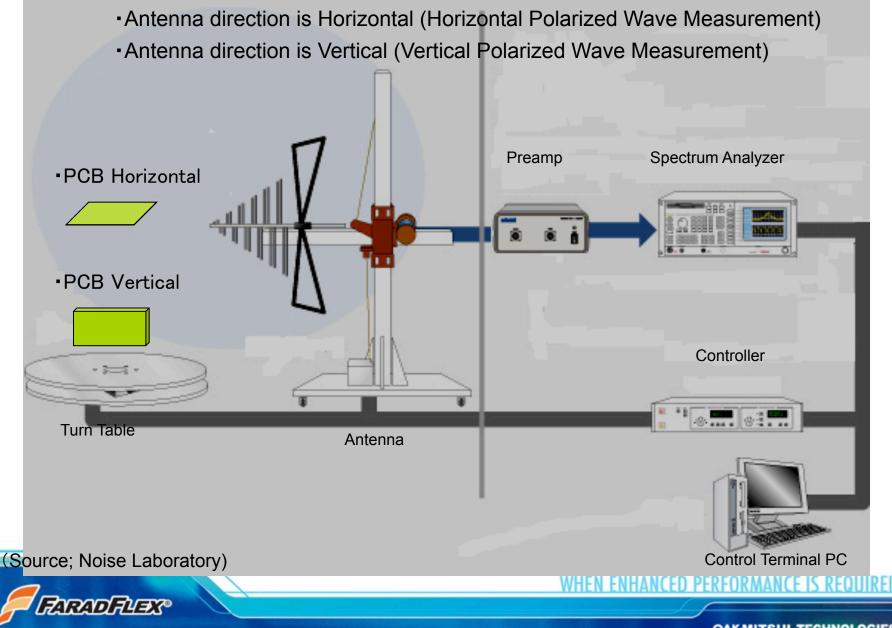

#### A Conception Diagram of The Distant Place Magnetic Field Measurement

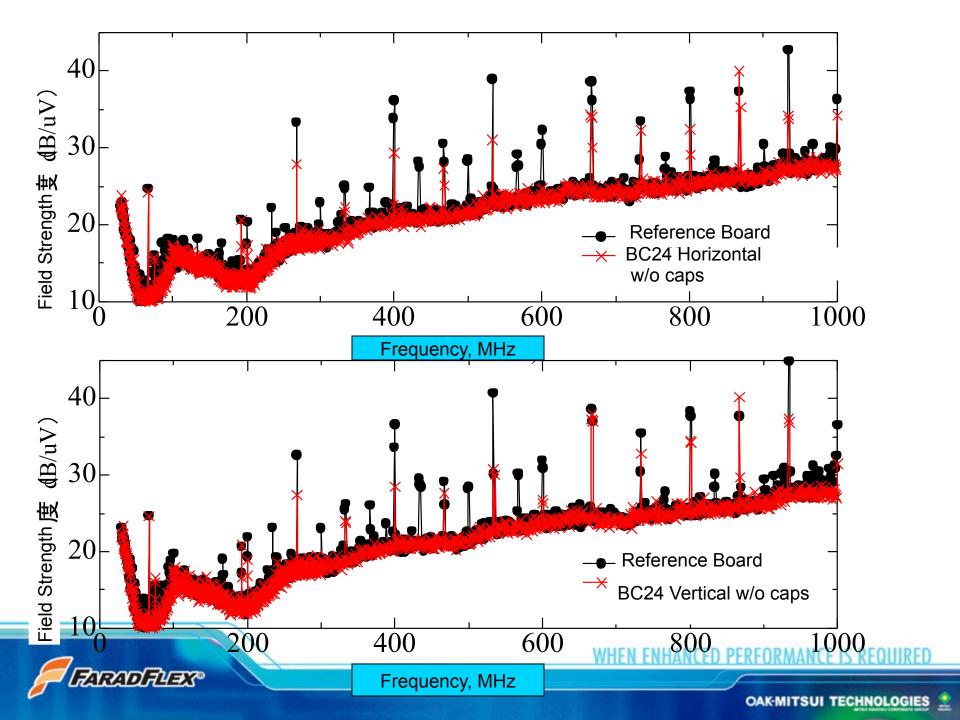

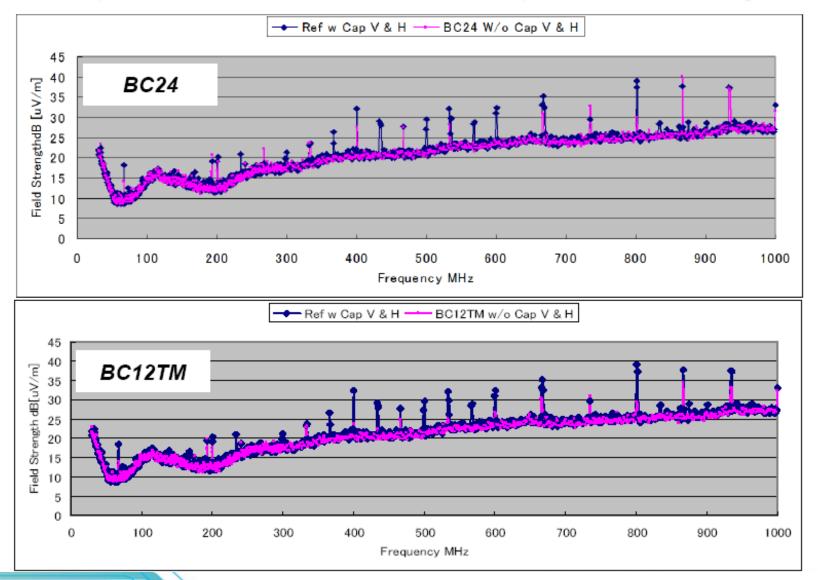

#### Comparison between reference board with Caps and BC without Caps

WHEN ENHANCED PERFORMANCE IS REQUIRED

### NCR-TERADATA CASE STUDY

WHEN ENHANCED PERFORMANCE IS REQUIRED

## **NCR-TERADATA Study**

|                                            |                                        | L1 – Signal ½ Oz    |                                            |

|--------------------------------------------|----------------------------------------|---------------------|--------------------------------------------|

|                                            | L1 – Signal ½ Oz                       | L2 – Power 1 Oz     | 3.3V                                       |

| 3.3V                                       | L2 – 3.3V Power 1 Oz                   | L3 – GND 1 Oz       | Embedded Material                          |

|                                            | L3 – Signal 1 Oz                       | ► L4 – Signal 1 Oz  |                                            |

|                                            | L4 – GND 1 Oz                          | L5 – GND 1 Oz       |                                            |

|                                            | L5 – Signal 1 Oz                       | ► L6 – Signal 1 Oz  |                                            |

| 1.5V                                       | L6 - 48V, 12V_A, 1.5V Power 1 Oz       | L7 – Power 1 Oz     | 1.5V                                       |

|                                            | L7 – GND 1 Oz                          | ► L8 – GND 1 Oz     |                                            |

|                                            | L8 – Signal 1 Oz –                     | ► L9 – Signal 1 Oz  |                                            |

|                                            | L9 - 1.5V, 1.8V, VCC, 12V_B Power 1 Oz | L10 – GND 1 Oz      |                                            |

|                                            | L10 – Signal 1 Oz                      | ► L11 – Signal 1 Oz |                                            |

| 1.5V                                       | L11 – GND 1 Oz                         | L12 - Power 1 Oz    | 1.5V                                       |

|                                            | L12 – Signal ½ Oz                      | L13 – GND 1 Oz      | Embedded Material                          |

| Current Stackup                            |                                        | L14 – Signal ½ Oz   |                                            |

| Total Copper:<br>Power – 3oz<br>GND – 3 oz |                                        |                     | Emb Capacitance Stackup                    |

|                                            | 781 0.1µF decou                        | pling capacitors    | Total Copper:<br>Power – 3oz<br>GND – 5 oz |

|                                            |                                        | WHEN ENHANC         | ED PERFORMANCE IS REQUI                    |

| FARADFLEX®                                 |                                        |                     |                                            |

|                                            |                                        |                     | OAK-MITSUI TECHNOLO                        |

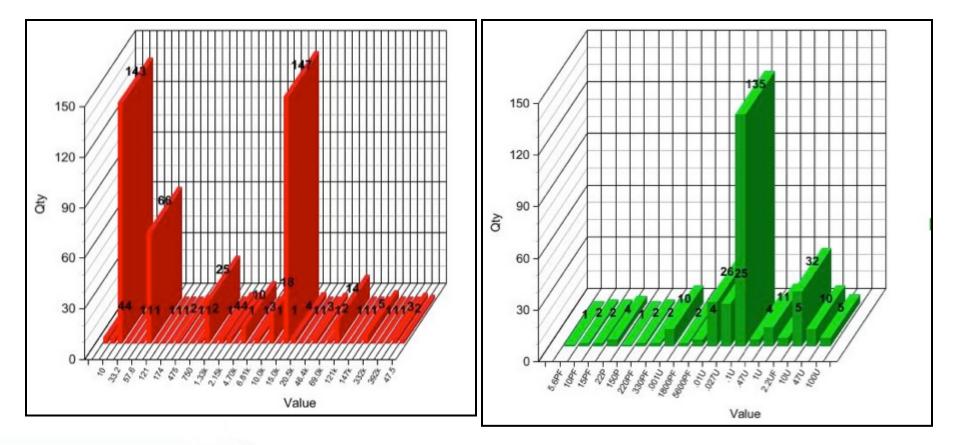

## **Capacitance Measurements**

(courtesy of Univ. of Missouri at Rolla)

| Plane Pair | FR-4 (nF)                | BC24 (nF)     | BC12 (nF)              | BC12TM (nF)        |

|------------|--------------------------|---------------|------------------------|--------------------|

| 1.5V/GND   | <mark>76.1</mark> (75.8) | 179.5 (179.0) | 286.7 (266)            | 487 (478)          |

| 3.3V/GND   | <mark>21.2 (21.2)</mark> | 323.8 (321.3) | <mark>551 (541)</mark> | <b>1148 (1082)</b> |

From LCR Meter

Extracted from VNA

Note: 1.5V plane is split resulting in smaller capacitor area

Replaces **78.1**  $\mu$ F of capacitance on standard board (781 capacitors of 0.1  $\mu$ F)

VHEN ENHANCED PERFORMANCE IS REQUIRED

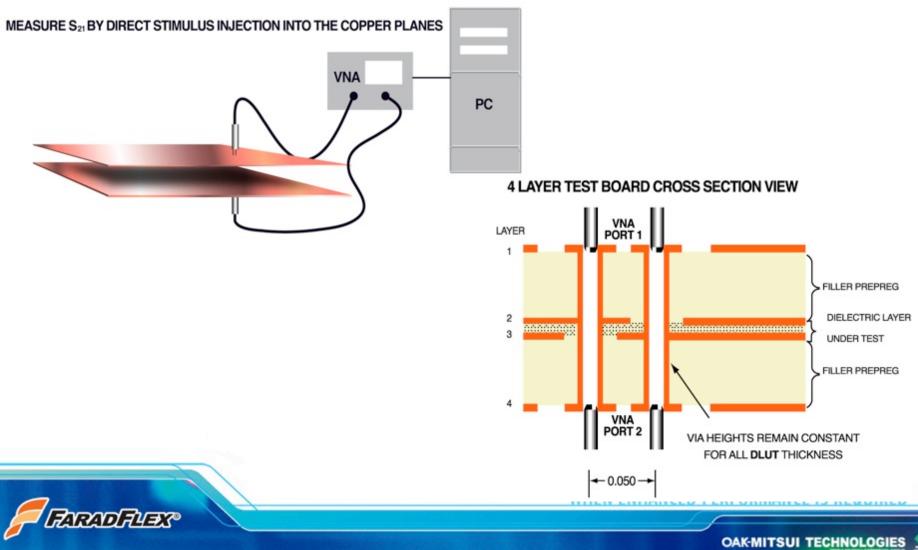

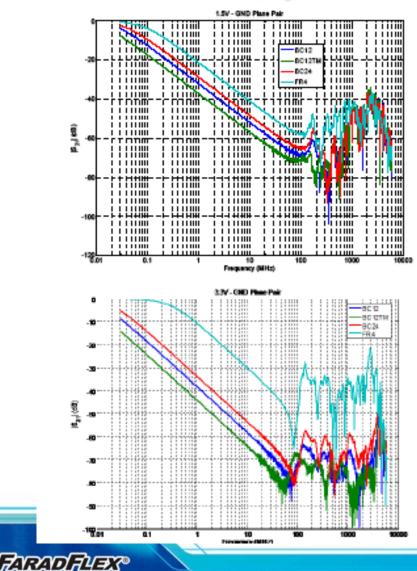

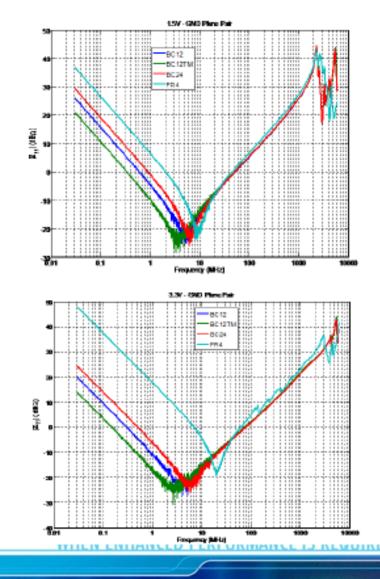

### **Board Impedance Measurements (S21, Z11)**

Measurement Equipment : Agilent 8753D (Vector Network Analyzer)

Probe Point : Decoupling Capacitor Pad

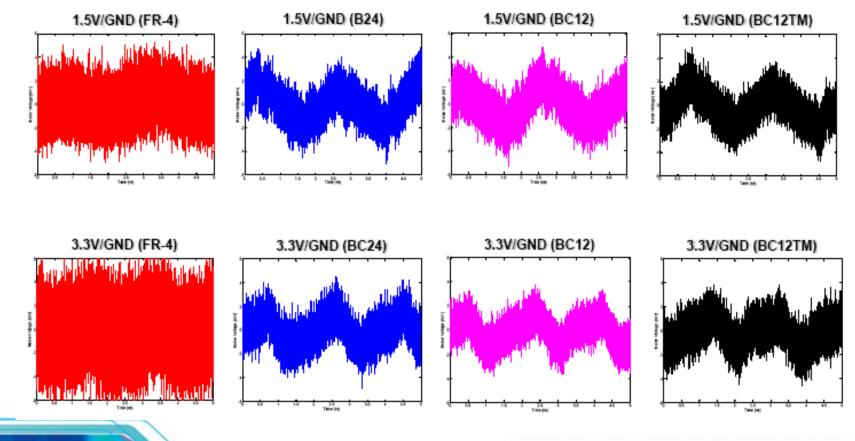

## **Time Domain Power Bus Noise Measurement**

Measurement Equipment : Agilent Infiniium 54855A (Digital Sampling Oscilloscope) Probe Point : Decoupling Capacitor Pad

WHEN ENHANCED PERFORMANCE IS REQUIRED

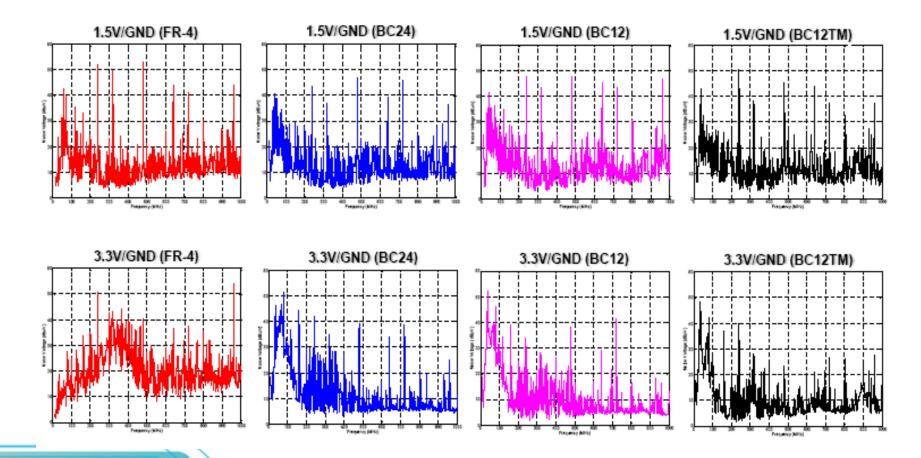

## **Frequency Domain Power Bus Noise Measurement**

Measurement Equipment : Agilent E7404A (Spectrum Analyzer)

Tested to 1 GHz

#### Probe Point : Decoupling Capacitor Pad

WHEN ENHANCED PERFORMANCE IS REQUIRED

### HARRIS CASE STUDY

WHEN ENHANCED PERFORMANCE IS REQUIRED

HARRIS CORPORATION RF Communications Division

#### The Embedded Passives Journey

#### IPC/APEX – April 2, 2008 Authors:

Bill Devenish – Harris Corp., Mechanical Advanced Development (MAD) Andrew Palczewski – Harris Corp., PCB Technologist

WHEN ENHANCED PERFORMANCE IS REQUIRED

HARRIS CORPORATION

**RF** Communications Division

Used with the permission of Harris Corporation

OAK-MITSUI TECHNOLOGIES

CED PERFORMANCE IS REQUIRE

| COST SAVINGS      | \$37.88 |

|-------------------|---------|

|                   |         |

| -Part Cost        |         |

| CAPACITORS        | \$1.19  |

|                   |         |

| RESISTORS         | \$9.77  |

|                   |         |

|                   |         |

| - Cost of Quality |         |

| Component         | Body    |

| CAPACITORS        | \$4.04  |

|                   | 0603    |

|                   | 0402    |

|                   |         |

| RESISTORS         | \$11.06 |

|                   | 0201    |

|                   | 0402    |

|                   |         |

| -Assembly Cost    | \$11.82 |

| Total Parts       | 591     |

FARADFLEX

Used with the permission of Harris Corporation

WHEN ENHANCED PERFORMANCE IS REQUIRED

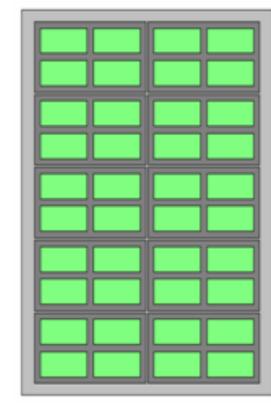

## **Original Panelization - 16 Up**

#### Size:

Panet 18.0 x 24.0 Array: 5.6 x 5.524 Part 4.54 x 2.15

#### Panel Yield:

8 Arrays of 2 Parts 16 Parts Total 57.3% Material Utilization

#### Matrix:

On Panet 2 x 4, Origin: X3.35 Y0.800 On Array: 1 x 2

#### Spacing:

On Panet: 0.1 x 0.1 On Array: 0.1 x 0.1

#### Panel Borders:

Left 3.35 Right 3.35 Top: 0.802 Bottom: 0.802

#### Array Borders: Left 0.53 Right 0.53 Top: 0.562 Bottom: 0.562

#### 0N689749-8 redux 25%

Size:

**Revised Panelization - 40 Up**

Panel: 18.0 x 24.0 Array: 8.0 x 4.42 Part: 3.4 x 1.61

#### Panel Yield:

10 Arrays of 4 Parts 40 Parts Total 81.9% Material Utilization

#### Matrix:

On Panet: 2 x 5, Origin: X0.95 Y0.75 On Array: 2 x 2

#### Spacing:

On Panet: 0.1 x 0.1 On Array: 0.4 x 0.4

#### Panel Borders: Let: 0.95 Right 0.95

Top: 0.75 Bottom: 0.75

#### Array Borders:

WHEN ENHANCED PERFORMANCE IS REQUIRED

Left 0.4 Right 0.4 Top: 0.4 Bottom: 0.4

Used with the permission of Harris Corporation

Courtesy of Harris Corp. and CALCE

## Other Benefits Of FaradFlex

WHEN ENHANCED PERFORMANCE IS REQUIRED

## Performance: Thermal Stability

Thinner dielectric provides better heat transfer to copper

VHEN ENHANCED PERFORMANCE IS REQUIRED

## Capacitor Material vs. FR4

| Properties                           | NiP/Capacitor<br>Core  | NiP Core<br>FR-4 (control) | Remarks and Conditions          |

|--------------------------------------|------------------------|----------------------------|---------------------------------|

| Sheet Resistivities (ohm/square)     | 25                     | 25                         | Nominal                         |

| Material Tolerance                   | +/-5%                  | +/-5 %                     |                                 |

|                                      |                        |                            | MIL-STD-202-108I                |

| Load Life Cycling Test               |                        |                            | Ambient Temp: 70C               |

| Resistor Size: 0.500" X 0.050"       |                        |                            | On Cycle: 1.5 hrs               |

| Loaded: (Δ R%) @ 150mW               | <0.9 after 3200 hrs.)  | <5                         | Off Cycle: 1.5 hrs              |

| Unloaded: $(\Delta R\%)$             | <0.74 after 3200 hrs.) |                            | Length Of Test: 10000 hrs       |

|                                      |                        |                            | MIL-STD-202-308                 |

| Current Noise Index in dB            | <-23                   | <-15                       | Voltage Applied: 5.6 Volts      |

|                                      |                        |                            | MIL-STD-202-103A                |

|                                      |                        |                            | Temp: 40 °C                     |

| Humidity Test ( $\Delta$ R%)         | 0.5                    | 0.5                        | Relative Humidity: 95%          |

|                                      |                        |                            | Time: 240 hrs                   |

|                                      |                        |                            | MIL-STD-202-304                 |

| Characteristic (RTC) PPM/°C          | (-6.0                  | 50                         | Hot Cycle: 25°, 50°,75° 125°C   |

|                                      |                        |                            | Cold Cycle: 25°, 0°,-25°, -55°C |

|                                      | $\langle \rangle$      |                            | MIL-STD-202-107B                |

| Thermal Shock ( $\Delta R\%$ )       | 0.2                    | -0.5                       | No of Cycles: 25                |

|                                      | $\langle \rangle$      |                            | Hot Cycle Temp: 125 °C          |

|                                      |                        |                            | Cold Cycle Temp: -65 °C         |

| Solder Float ( $\Delta$ R%)          |                        |                            | MIL-STD-202-210D                |

| After 1 Cycle                        | -0.4                   | 0.5                        | Temp: 260°C                     |

| After 5 cycles                       | -0.6                   |                            | Immersion: 20 Second            |

| Power Density (mW/mil <sup>2</sup> ) | 0.45                   | 0.15                       | Step-up Power Test              |

| derated at 50%                       | $\sim$                 |                            | Resistor size 0.020" x 0.030"   |

3X better power density through resistor due to better heat conductivity of FaradFlex

Courtesy of Bruce Mahler of Ohmega

### Synergistic Effect !

IANCED PERFORMANCE IS REQUIRE

## Conclusion

- Embedded Capacitor and can Improve System Price/Performance by

- Reducing Discrete Caps

- Reducing PWB size

- Increasing Functionality

- Improving power distribution

- Improving Signal integrity

- Thinner Power Distribution Planes are required for improved Impedance Performance at high frequency

- New Substrates have demonstrated *excellent* electrical performance and physical properties.

CED PERFORMANCE IS REQU

- They are *compatible* with PCB processing; a truly "drop in" material.

- Materials are commercially available from many Fabricators

- Substrates Filled with Ferroelectric Particles have better performance, but result in higher cost PCBs

- **GREEN** and Lead Free Solution

## FaradFlex ADVANTAGES

- **Broadest Line Up of Products**

- **Delivery is 1 week or less in US and Asia**

- **Local sales and technical support in US and Asia**

- Highest Quality Material compared with Competitive materials (no foreign material)

- Best Panel Size Flexibility for PCB Designs

- Most Copper Weight Options

- Lowest Profile Copper available used ONLY on FaradFlex

- Reliability: All panels HIPOT tested by Oak-Mitsui prior to shipment.

WHEN ENHANCED PERFORMANCE IS REQUIRED

Contact: <u>robert.carter@oakmitsui.com</u> john.andresakis@oakmitsui.com

# Additional information available at www.oakmitsui.com

VHEN ENHANCED PERFORMANCE IS REQUIRED