# Improving Power Delivery Networks (PDNs) Using Polyimide-based Thin Laminates

2017. 7. 19.

IPC

# Contents

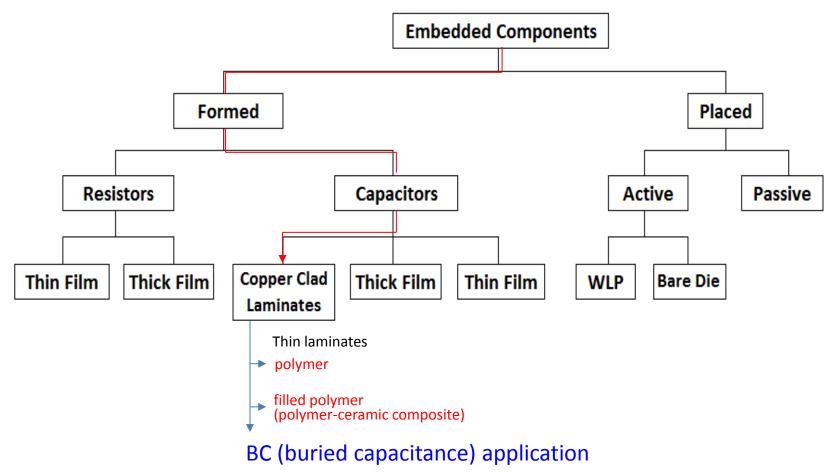

- 1. Embedded passives technology

- 2. Thin laminates: material choices and applications

- 3. Buried capacitance for power distribution network

- 4. Reliability and manufacturing process

- 5. Wrap-up

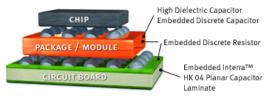

### Embedded passives technology

### **Embedded Passives Drivers**

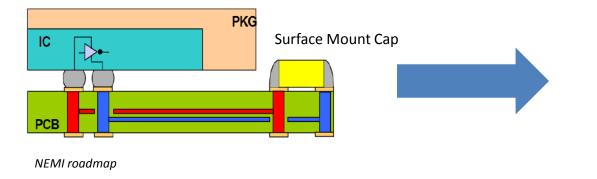

# Component density is reaching its limit.

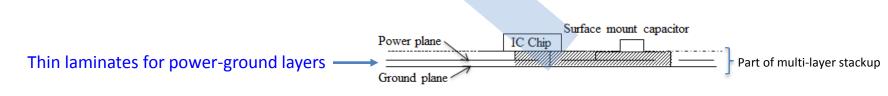

Mounting space limitation Larger current loop Vias and traces are inductive

Integrated capacitor has less parasitic inductance!

- $\rightarrow$  Field cancellation caused by opposing current

- $\rightarrow$  planar and in-plane, current loop is much smaller

Prof. Richard Ulrich

: A discrete or active component that is fabricated or inserted as an integral part of a printed board.

from 2013 IPC International Technology Roadmap

### Thin laminates: material choices and applications

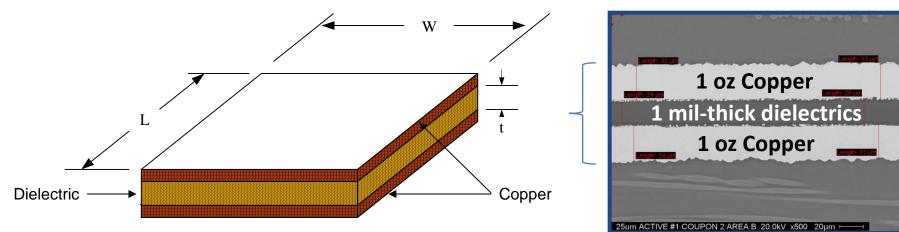

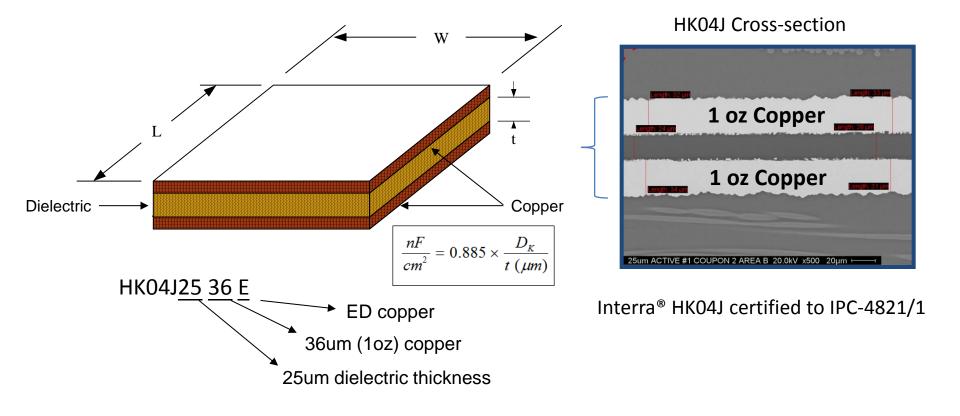

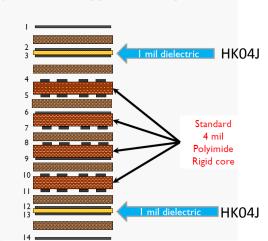

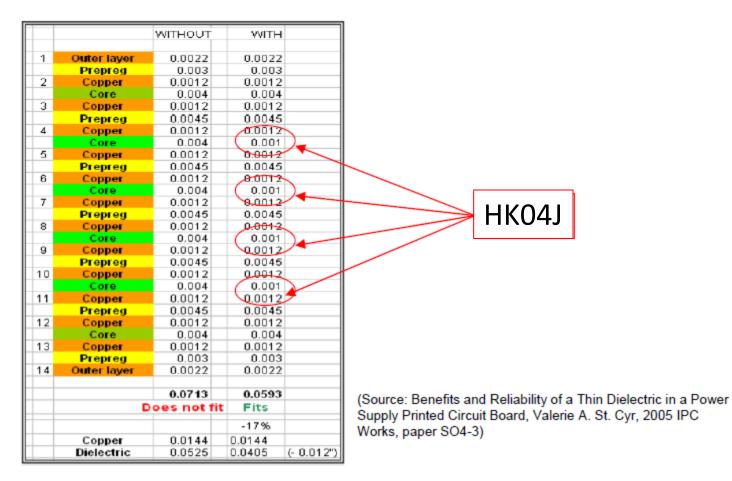

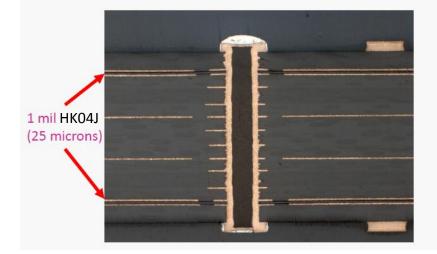

Cross-section

Dielectric thickness is 1mil (=25um) and below.

18 x 24 inch is standard size.

Cap. density,

$$nF/cm^2 = 0.885 \frac{k, \text{ the dielectric constant}}{\text{dielectric thickness, } \mu m}$$

( $nF/cm^2 \ge 0.45 = nF/in^2$ ) Prof. Richard Ulrich

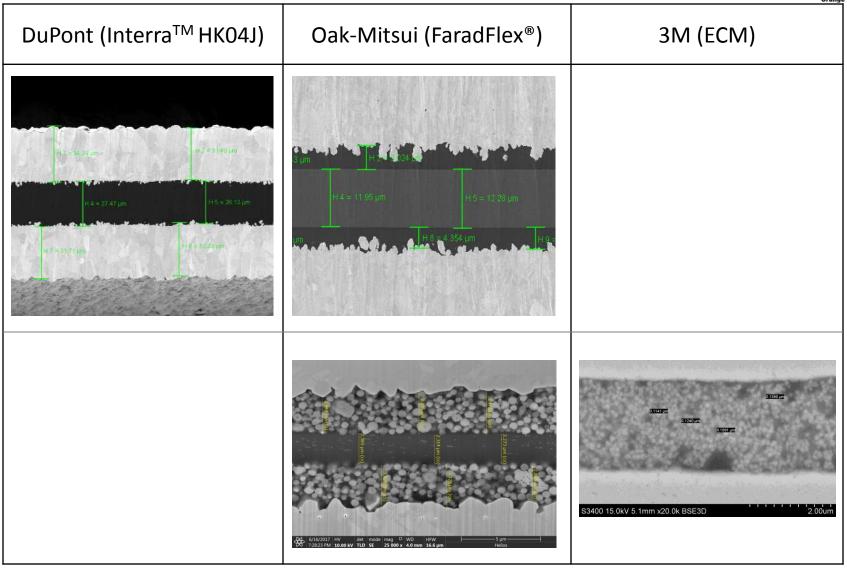

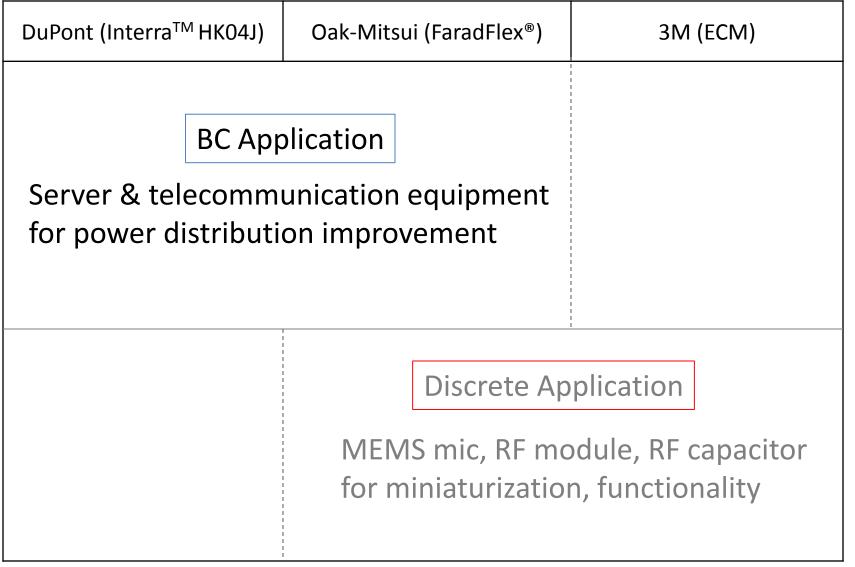

### **Thin Laminates : Material Choices**

## Thin Laminates for High Layer Count PCB

### QUPIND.

### High-end computing telecom industry

SUN's V890 server and its CPU module, which has 1 mil HK 04 on some of it's power rail, Source: Istvan Novak, SUN's Experience with Thin and Ultra Thin Laminates for Power Distribution Applications, DesignCon 2006, February 6-9, 2006

Thin laminates create very low inductance!

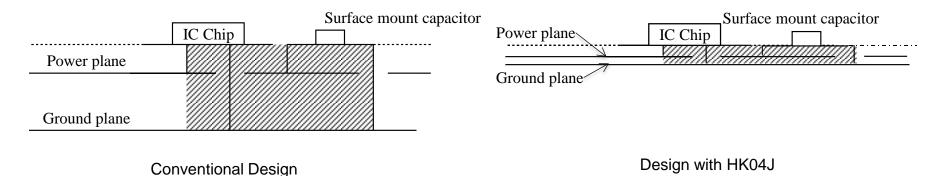

Design with HK04J

## HK04J comes in a dielectric thicknesses of 25 and 12 microns. Use HK04J to improve PDN design in high layer count PCB.

Image: Over size (i.e. 24 x 36 inch), unbalanced constructions are available.

IPC

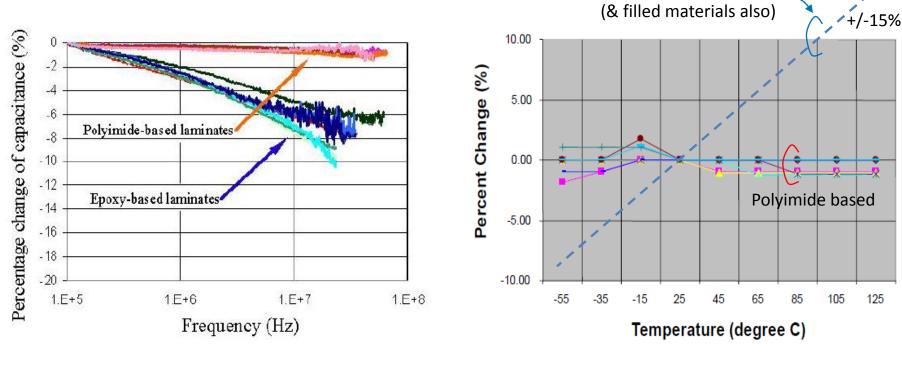

### Why Polyimide?

Capacitance Stability over Temp, Freq and Bias Voltage

from Sun Microsystems

\* TCC: Temperature coefficient of capacitance

**Epoxy based materials**

## Why Polyimide?

IPC

inners Counci

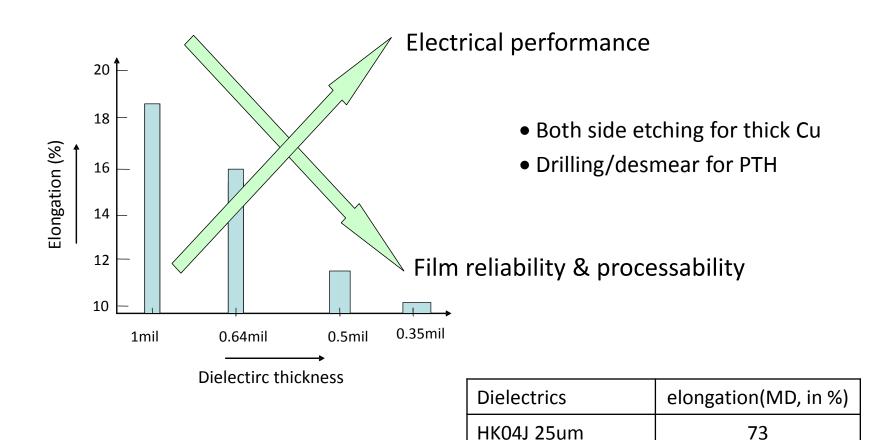

Dielectric film strength to optimize mechanical reliability and electrical performance

HK04J 8um

45

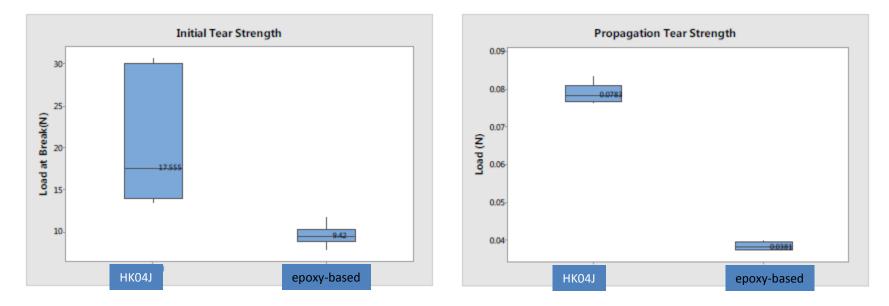

### Tear Strength Side by Side Comparison for 1mil-thick BC Core

Initial & propagation tear strength of polyimide-based dielectrics is almost double than that of epoxy-based materials which indicates robustness in manufacturing.

# Interra<sup>®</sup> HK04J Product Lineup

|                                          |                    | Interra® HK04J |         |          |      |

|------------------------------------------|--------------------|----------------|---------|----------|------|

| Laminate requirement                     | Units              | HK04J25        | HK04J12 | HK04J08* |      |

|                                          |                    | ED             | ED      | ED       | RA   |

| Dielectric thickness (nominal)           | μm                 | 25             | 12      | 8        | 8    |

| Peel strength                            | kN/m               | 1.8            | 1.4     | 3.2      | 4.7  |

| Capacitance, at 1MHz                     | pF/cm <sup>2</sup> | 125            | 260     | 411      | 384  |

| Thermal stress, 180sec at 288 $^\circ$ C | sec                | PASS           | PASS    | PASS     | PASS |

| BDV (breakdown voltage)                  | kV                 | >5             | 3-4     | 1.6      | 1.8  |

\* Product under development – Initial data, based on using 2oz copper

\* 8u core is not commercialized but was made off our commercial line using the same process to make standard HK04J product.

### Buried capacitance for power distribution network

### **PDN Function**

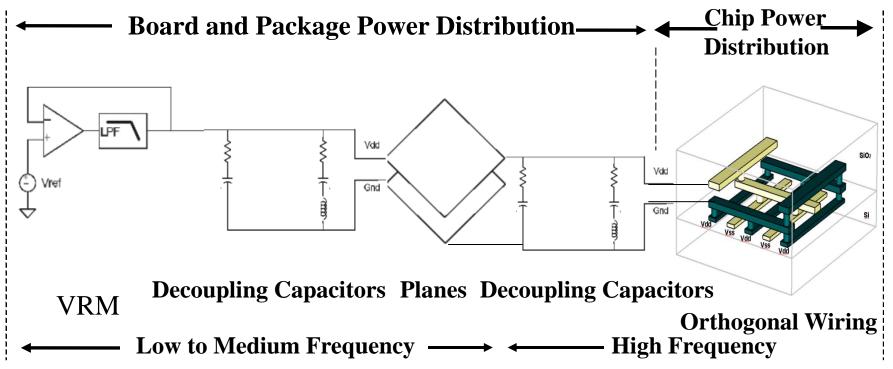

- ✤ PDN, power distribution network delivers power to ICs and other active circuits.

- Provide a return path for signals.

- PDN consists of a power supply, circuit traces, capacitors, power and ground planes, capacitors and an IC or some other active silicon

- At frequencies from as low as 100kHz the dielectric that separates power and ground planes begins strongly influencing PDN performance.

- ✤ A typical PDN looks like this :

IPC

## Why HK04J Improves PDN Performance?

- Capacitors in the past have been placed on the surface of the board in parallel to reduce the capacitor bypass inductance

- The capacitance density of the thin power and ground plane laminate is very low and does not come close to matching the total capacitance of the SMT caps

- So, why does HK04J allow you to remove capacitors from the surface of the board and save money?

- HK04J reduces the plane spreading inductance and reduces modal resonances

The number of capacitors needed is less – improved escape routing, increased yield by reducing assembly defect.

There is much more flexibility in where the capacitors are placed (i.e. improved circuit density).

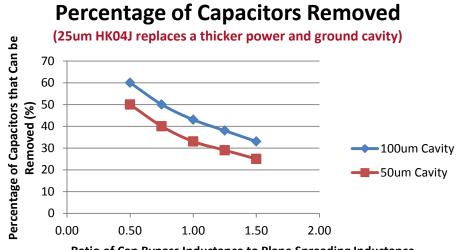

### How Many SMT Capacitors Can I Remove?

- Estimate the capacitor bypass and plane spreading inductances. Divide the bypass inductance by the plane spreading inductance to get a factor.

- The graph shows how many capacitors can be removed from your design

Example: If the original design uses a 100um power and ground cavity that is replaced with a 25um HK04J cavity, the percentage of capacitors that can be removed will be 43% if the ratio of the capacitor bypass network inductance to plane spreading inductance is 1.0.

**Ratio of Cap Bypass Inductance to Plane Spreading Inductance**

## How Many SMT Capacitors Can I Remove?

# **POWER DISTRIBUTION NETWORK**

Different dielectric thicknesses and the total amount of capacitors needed to

#### achieve target impedance of 0.02 Ohms:

Total Caps = 84

Total Caps = 35

Dielectric Thickness = 10 mil

Dielectric Thickness = 4 mil

yers, 1/2 OZ copper on all layers

Dielectric Thickness = 5 mil

Dielectric Thickness = 3 mil

© 2017 Lockheed Martin Corporation. All Rights

# of Caps vs Laminate Thickness

Total Caps = 42

Total Caps = 33

Dielectric Thickness = 1 mil

Total Caps = 19

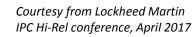

### HK04J reduces inductance and reduces modal resonances.

### **Electrical Performance**

IPC

Designers Council

### Interra® HK04J reduces impedance

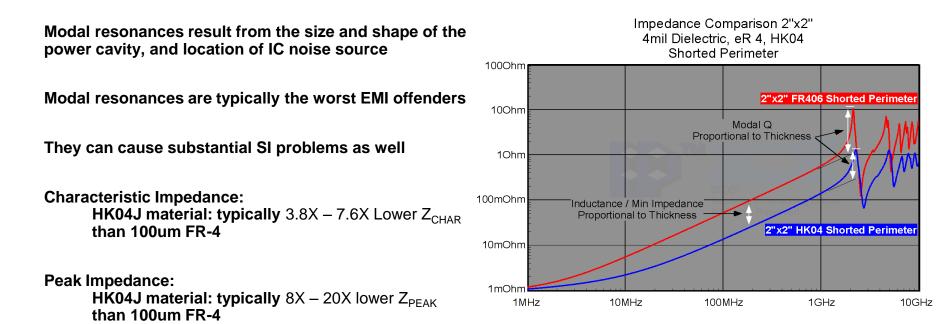

Impedance Testing set-up for SUN's V890 server CPU module

Comparison of impedance b/w 2-mil FR-4 and 1-mil HK04 at one of the test points on the bare CPU module board.

Example from a Sun V 890 server CPU module showing reduce impedance and resonance. Source: Istvan Novak, "Embedded Capacitance and Embedded Capacitors: Overview of Modeling and Applications" at DesignCon 2006, Feb 6-9, 2006, Santa Clara, CA

### **Electrical Performance**

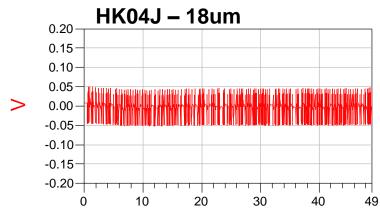

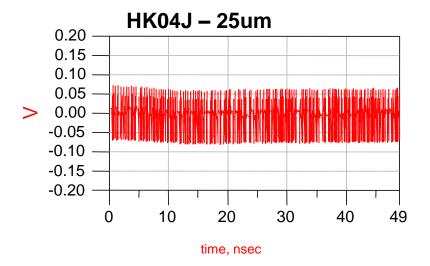

SSN dramatically reduced on 6 layer board with HK04J

time, nsec

time, nsec

| Material       | SSN (peak) |

|----------------|------------|

| HK04J – 18um   | 50mV       |

| HK04J – 25um   | 65mV       |

| BC2000 – 2mils | 150mV      |

1 mil (25  $\mu m$ ) HK04J provides large reductions in SSN versus 2 mil BC2000

### **Electrical Performance**

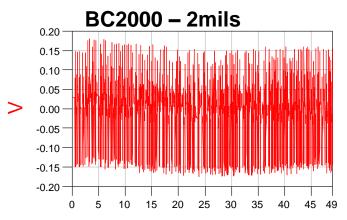

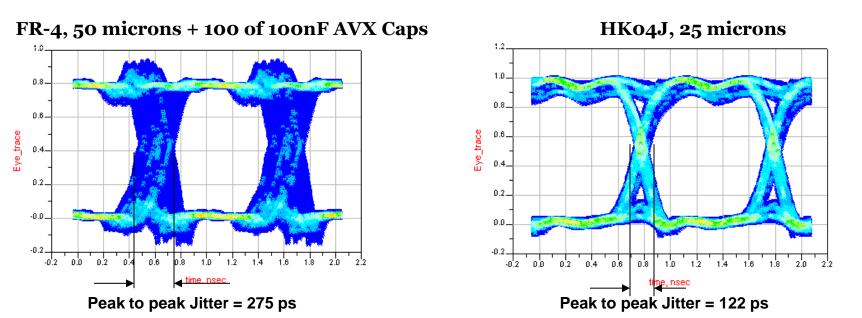

### In Addition to Improved PDNs HK04J Improves Signal Integrity

Simulation confirmed comparison impact on eye-opening for above two cases:

Assumptions: Similar to Server Front Side Bus

- Link Speed = 1 Gbps

- Number of lanes = 16 bit

- Line Type = Stripline, Single Ended, 50 Ohms

- Voltage swing: 1V

- Trise/Tfall = 300 ps

- Termination = 100 Ohms to both Gnd and Vdd

- Datastream = PRBS

IPC

**Designers** Council

### **Reducing Board Thickness**

# Reduce board thickness or add thicker Cu layers, for the same thickness

Example of a 14-layer board using 4 layers of 1-mil HK04J compared to that using 4 layers of 4-mil FR-4, reducing board thickness by 12 mils, and helping the PWB meet a 0.060 mil thickness requirement.

IPC

Designers Council

## **Reducing Overall Cost**

## Interra<sup>™</sup> HK04 helps reduce total cost

- 1. Reduce the number of capacitors:

- Typically, 30-50 % of existing capacitors can be removed

- Typical cost: 0.5 cents per capacitor + 1.2 cents assembly, rework/yield loss.

- Example:

- 30-layer count PCB with 3000 caps  $\rightarrow$  2000 caps = \$ 17 savings.

- 2. Reduce the number of PTH

- Typically, 0.08 cents per PTH; 2 PTH per cap.

- Example:

- 30-layer count PCB with 3000 caps → 2000 caps = 2000 PTH saved

= \$ 1.6 saved

- 3. Reduce signal-layers by reducing capacitors around a dense layer constraining BGA.

- Example:

- 24-layer count PCB → 22-layer count PCB = \$ 140-160 savings per panel.

- 4. Reduce PTH aspect ratio:

- Replace thicker Power/Ground layers, 4-mil FR-4 → 1 mil HK 04 = 3 mils savings.

- Reduce signal layer count.

- Impact:

- 9-12, 0.5 % yield per unit aspect ratio improvement

- 12-15, 1 % yield per unit aspect ratio improvement

- 15-18, 2 % yield per unit aspect ratio improvement

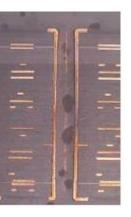

Top view of a PCB with a dense BGA (GPU)

Bottom view of a PCB: Note the dense array of SMTs that can block routing.

IPC

### The design demands high performance:

When lower impedance is required from 300MHz to 800MHz (or higher) than is possible with thicker dielectric

### The existing design is too expensive:

In high volume mfg HK04J 25um saves money if the original design has more than 3-4 caps / sq in In medium volume mfg HK04J 25um saves money at even lower original capacitor densities

### The existing capacitor bypass network is too big:

HK04J 25um typically removes > 40% of the bypass capacitors HK04J 25um removes even more capacitors in high performance designs

### Reliability and manufacturing process

### HK04J Shows Proven Reliability

| Test                                                | Method/Conditions                                            | Results                                                                             |

|-----------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Humidity, Temperature, Bias<br>Testing, 85/85       | 85ºC/85% RH for 1000 hours, 100<br>VDC bias                  | Passed with no change in resistance. Resistance under conditions $\text{E10}\Omega$ |

| Humidity Temperature Bias Testing,<br>HAST          | 120°C/90% RH, 2.0 atm pressure<br>for 69 hours, 100 VDC bias | Passed with no change in resistance. Resistance under conditions $\text{E8}\Omega$  |

| Moisture and Insulation Resistance, M&IR            | IPC TM-650 2.6.3.2                                           | Passed. Resistance E11 $\Omega$                                                     |

| Temperature Coefficient of<br>Capacitance, TCC      | From –25°C to 125°C                                          | Variation less than 5% over range. –<br>15ppm/ºC                                    |

| Humidity Coefficient of Capacitance                 | 0 to 90% RH                                                  | Increase less than 10% from 0 to 90% RH                                             |

| Capacitance Change with 85/85<br>Aging              | 85°C/85% RH for 1000 hours                                   | Capacitance unchanged during aging                                                  |

| Peel Strength Change after Solder<br>Float          | Solder float 288°C, 10 sec                                   | No change in peel strength                                                          |

| Peel Strength Change with 85/85<br>Aging            | 85°C/85% RH for 1000 hours                                   | Peel strength > 6 pli (1N/mm) after<br>1000 hours                                   |

| Peel Strength Change with High<br>Temperature Aging | Bake at 150°C for 1000 hours                                 | No change in peel strength                                                          |

| Peel Strength Change with Thermal<br>Cycling        | -55°C to 150°C for 1000 hours                                | No change in peel strength                                                          |

### Interra<sup>™</sup> HK04J Reliability

# Reliability tests conducted by major PWB fabricator (using HK04J in commercial volumes)

| NO. | TEST<br>ITEM             | TEST<br>CONDITION                                                                                         | ACCEPTANCE                                                                              | TEST<br>RESULT                         | SAMPLE |

|-----|--------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------|--------|

| 1   | THERMAL<br>STRESS        | PER IPC-TM-<br>650,METHOD 2.6.8<br>288°C±5°C<br>10~11SEC.<br>6CYCLES                                      | PER IPC-6012B,3.6                                                                       | NO<br>SEPARATION<br>NO CORNER<br>CRACK | 4 PCS  |

| 2   | THERMAL<br>SHOCK         | PER IPC-TM-<br>650,METHOD 2.6.7.2<br>AIR TO AIR - 55℃ →<br>125℃<br>15MIN 15MIN<br>TOTAL 400 CYCLES        | MICROSECTION MUST<br>HAS NO<br>CRACK,DELAMINATIO<br>N,BARREL CRACK AND<br>IP-SEPARATION | PASS                                   | 2 PCS  |

| 3   | PRESSURE<br>COOKIER TEST | TEST CONDITION :<br>121°C,100%RH,168H<br>PRESSURE : 2<br>KGF/CM <sup>2</sup><br>TEST VOLTAGE : 100<br>VDC | MICROSECTION MUST<br>HAS NO<br>CRACK,DELAMINATIO<br>N,BARREL CRACK AND<br>IP-SEPARATION | PASS                                   | 2 PCS  |

| 4   | INFRA-RED<br>REFLOW      | LEAD-FREE PROFILE<br>(260°C)<br>6 CYCLES                                                                  | PER IPC-6012B,3.10.8                                                                    | NO<br>DELAMINATION                     | 3 PCS  |

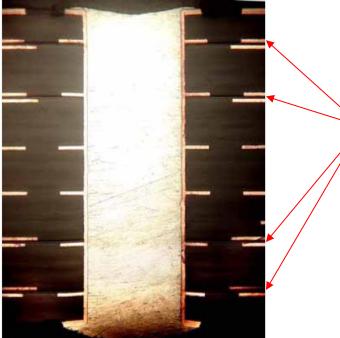

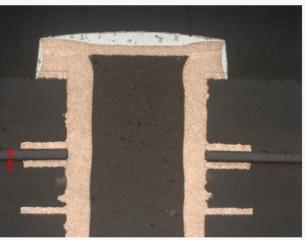

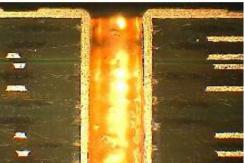

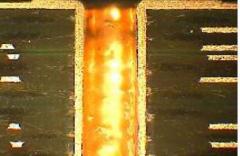

22L PWB with 2 layers of HK04J, after 6x thermal stress

22L PWB with 2 layers of HK04J, after 400 cycles of thermal shock

IPC

Designers Council Orange County Chapter

### Interra<sup>™</sup> HK04J Reliability

Designers Council Orange County Chapter

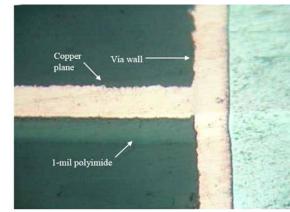

1 mil HK04J2536

Cross-section of PTH with 1 mil HK04J after 6 X solder float. No damage to the PTH. Source: *Istvan Novak*, SUN's Experience with Thin and Ultra Thin Laminates for Power Distribution Applications, DesignCon 2006, February 6-9, 2006

Courtesy from Lockheed Martin IPC Hi-Rel conference, April 2017

### Interra<sup>™</sup> HK04J Manufacturing

### IPC Designers Council

## Interra<sup>™</sup> HK04 Manufacturing: Overview

### Processes on equipment capable of running 2-mil FR-4.

- Does NOT Require front-edge leaders at develop/etch/strip

- Vertical Racked Black-oxide acceptable ٠

- No puncturing of clearance holes (anti-pads) during inner-layer processing. ٠

- \* Thin material processing equipment required

\* Does require scale characterization

### Double Side Processing

- One pass through the inner-layer process \* Not requiring sequential lamination

- PTH electroless and electroplating process = Standard

### HK04 scales consistently and scale-factors are comparable to that of 2-mil FR-4

- Dimensional Stability (mils/inch): ٠

- Warp (MD): HK 04, Avg.: -0.16,  $\sigma$  = 0.18 vs. ZBC 2000, Avg.: 0.93,  $\sigma$  = 0.11

- Fill (TD): HK 04, Avg.: -0.36,  $\sigma$  = 0.14 vs. ZBC 2000, Avg.: 0.8,  $\sigma$  = 0.16

#### Typical yields are significantly better than that of 2-mil FR-4

- HK04 Inner Layer Yield (after HiPot), Typically = 99 % vs. 2-mil FR-4 = 85-97 %

- HK04 Final process yield, typically = 98 %, vs. 2-mil FR-4 = 85-97 %

- Processing costs similar to that of 2-mil FR-4

Cross-section of a PTH plated using standard electroless/electroplating process

## **Processing Guidelines**

| Process – step       | Guideline                                    | Special concerns, if any and resolutions                                                                                                                                                 | Typical<br>Yield |

|----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Preclean/ Lamination | Thin core equipment<br>required – no leaders | <ul> <li>Surface Cleaning = standard</li> <li>Need to be careful that the chain grippers<br/>on the roller coat line dryer don't tear<br/>through the edges for the material.</li> </ul> | 99+%             |

| Expose               | Standard Process                             | No Known Issues                                                                                                                                                                          | 99+%             |

| Develop, Etch, Strip | Thin core equipment required, no leaders     | No Known Issues                                                                                                                                                                          |                  |

| Post Etch Punch      | Front/ Manual Unloading<br>Required          | No issues with the cameras on etched fiducials.                                                                                                                                          | 99+              |

| AOI                  | Standard Process                             | No Known Issues                                                                                                                                                                          |                  |

| Oxide                | Horizontal or vertical acceptable            | Extra care when lowering layers in slots so the layers don't dent on bottom of basket.                                                                                                   | 99+              |

| Lay-up               | Standard Process                             | No known issues. Core less likely to<br>fracture than woven cores.                                                                                                                       | 99+              |

### Wrap-up

### **Presentation Summary**

- Power needed when an IC chip turns on is delivered by the capacitors mounted near the chip.

- Reducing the inductance associated with the power delivery network results in many good things.

- Primary advantages are a reduced # of SMT caps required for your design and improved reliability.

### **HK04J Benefits Summary**

- Fewer plated through holes due to fewer SMT capacitors

- Improved routing capability

- Probable layer count reduction

- Lower power and ground noise

- Reduced simultaneous switching noise

- Improved signal integrity

- No glass bundles no CAF issue

- Reduced board thickness

Designers Council

### **Detailed Technical Discussion, Please Contact to :**

Jin-Hyun Hwang

Jin-Hyun.Hwang@dupont.com

(919) 248-5024

### **THANK YOU**

The miracles of science™