# THE PC December 2015 December 2015 MAGAZINE

an I·Connect007 publication

IPC Designers Council: Serving PCB Designers for Almost 25 Years p.10

McCurdy: How to Build a Successful IPC Designers Council Chapter p.18

IPC Designers Council Viewpoint: Gary Ferrari p.24

Much More!

# **INSIDE THE IPC DESIGNERS COUNCIL**

# **PCB BUYERS**compare nearly 1900 manufacturers now at The PCB List.

**Quick Search**

Advanced Search

The best way to find a PCB fabricator, anywhere.

### www.thepcblist.com

# **ATTENTION BUSINESS OWNERS:**

### CLICK HERE TO TAKE THE BizBrain IQ TEST

#### THIS MONTH'S FEATURE ARTICLES

### **The Designers Council Issue**

It's been almost 25 years since the first Designers Council meeting in Atlanta. Now, the council has chapters around the world, with thousands of members. This month, we bring you interviews with some of the people who helped make the Designers Council what it is today: Gary Ferrari, Anne Marie Mulvihill, Rick Hartley, Mike Creeden, and Scott McCurdy. Happy holidays!

#### 10 IPC Designers Council: Serving PCB Designers for Almost 25 Years

Interview with Anne Marie Mulvihill

#### 18 McCurdy: How to Build a Successful IPC Designers Council Chapter

By Judy Warner

24 IPC Designers Council Viewpoint: Gary Ferrari Interview

28 IPC Designers Council Viewpoint: Rick Hartley Interview

32 IPC Designers Council Viewpoint: Mike Creeden Interview

# Low-loss Laminate Materials for RF/Microwave/Millimeter-wave Designs

For over 100 years, Isola has been driving technology forward while improving end-product design with topperforming laminate and prepregs.

Our legacy continues with global R&D pushing our product line to the forefront in demanding RF/microwave designs.

With 10 manufacturing sites around the world, global quickturn capability, world-class technical service, measurement & modeling capabilities, and industry leading material development capabilities – Isola is well positioned to be your preferred RF/microwave partner. The newest members of Isola's growing RF/Microwave laminate family now includes Terra Green<sup>™</sup>, a halogen-free, very low-loss, thermoset material that is available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

Astra®MT is a revolutionary ultra low-loss thermoset laminate replacement for PTFE, suitable for automotive radar, mm-wave and AESA applications.

I-Tera MT is available in core thicknesses from 0.002" to 0.018" and offers 18 different prepregs for optimal design flexibility.

I-Tera<sup>®</sup>MT RF is available in 20 and 30 mil cores and a 3.38 and 3.45 Dk.

|                                                                                                                                                                                                                                              | TerraGreen™     | Astra <sup>®</sup> MT | I-Tera <sup>®</sup> MT/<br>I-Tera MT RF | IS680                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------------------------|------------------------------------------|

| Tg                                                                                                                                                                                                                                           | 200°C           | 200°C                 | 200°C                                   | 200°C                                    |

| Td                                                                                                                                                                                                                                           | 390°C           | 360°C                 | 360°C                                   | 360°C                                    |

| DK @ 10 GHz                                                                                                                                                                                                                                  | 3.45            | 3.00                  | 3.45                                    | 2.80 - 3.45                              |

| Df @ 10 GHz                                                                                                                                                                                                                                  | 0.0030          | 0.0017                | 0.0031                                  | 0.0028 - 0.0036                          |

| CTE Z-axis (50 to 260°C)                                                                                                                                                                                                                     | 2.90%           | 2.90%                 | 2.80%                                   | 2.90%                                    |

| T-260 & T-288                                                                                                                                                                                                                                | >60             | >60                   | >60                                     | >60                                      |

| Halogen free                                                                                                                                                                                                                                 | Yes             | No                    | No                                      | No                                       |

| VLP-2 (2 micron Rz copper)                                                                                                                                                                                                                   | Standard        | Standard              | Available                               | Available                                |

| Stable Dk and Df over the temperature range                                                                                                                                                                                                  | -55°C to +125°C | -40°C to +140°C       | -55°C to +125°C                         | -55°C to +125°C                          |

| Optimized Global constructions for Pb-Free<br>Assembly                                                                                                                                                                                       | Yes             | Yes                   | Yes                                     | Yes                                      |

| Compatible with other Isola products for<br>hybrid designs                                                                                                                                                                                   | Yes             | Yes                   | Yes                                     | For use in double-<br>sided applications |

| Low PIM < -155 dBc                                                                                                                                                                                                                           | Yes             | Yes                   | Yes                                     | Yes                                      |

| NOTE: Dk Df is at one resin %. The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms and conditions |                 |                       |                                         |                                          |

NOTE: Dk Df is at one resin %. The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms and conditions of the agreement under which they are sold.

#### FREE WEBINAR

PCB Material Selection for RF/Microwave/Millimeter-wave Design

This webinar will educate you on how to select the appropriate PCB material for RF, microwave and millimeterwave applications through careful consideration of cost constraints and system-performance parameters, such as the frequency of operation and bandwidth, the electrical size of board and its critical features, loss and uniformity requirements, temperature range of system operation, and thermal and processing considerations.

# www.isola-group.com/RF

DECEMBER 2015

VOLUME 4

NUMBER 12

thepcbdesignmagazine.com

an IConnect007 publication

THE OPTIMUM MAGAZINE DEDICATED TO PCB DESIGN

### TABLE OF CONTENTS

#### SHORTS

9 Quantum Physics Problem Proved Unsolvable

- 22 Nanostructured Metal Coatings Let the Light through for Electronic Devices

- **42** University of Twente Develops Versatile Method for Developing New Materials

- 58 New Nanomanufacturing Technique Advances Imaging, Biosensing Technology

- 71 Future Batteries Could Charge in 30 Seconds

#### HIGHLIGHTS

36 2015's Most-Read Design News

- 60 2015's Most-Read Articles

- 76 PCBDesign007 News

#### DEPARTMENTS

- **78** Events Calendar

- 79 Advertiser Index & Masthead

# STRVING FOR EXCELLENCE IN EVERYTHING WE SAY AND DO.

- Prototype to Production

- Time Critical Production

- Commitment to Customer Service

- Best Quality & Delivery Performance

- Fair and Competitive Pricing/Costs

- Rapid Response to Quote Requests

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

**Tour our Facilities**

View our Capabilities

The Absolute Best Value in High Technology Circuit Boards 847.891.5800 • www.eagle-elec.com

MANUFACTURERS OF QUALITY PRINTED CIRCUIT BOARDS

# The Designers Council: **Elevating PCB Design, and Designers**

IPC

Öo

Designers

by Andy Shaughnessy I-CONNECT007

#### It was a different time.

When the seeds of the Designers Council were first sown in 1991, PCB designers were still considered red-headed stepchildren, earning less respect than Rodney Dangerfield. The PCB was seen as just an interconnect platform, soulless and boring. And PCB designers were dinosaurs toiling away on a "mature" technology that would soon be replaced by multichip modules, or some other cool technology.

Back then, the integrated circuit was king; IC design was considered "sexy" and IC designers were the rock stars of electronics design. (Years ago, I told that story to a newly hired assistant editor, a cute 22-year-old girl right out of college. She said, "I have bad news for you: Nothing about this industry is 'sexy.'") But the lowly PCB designer was looked down upon by evervone.

It didn't help that PCB designers were spread out across so many various segments of the electronics industry. It's a vertical occupation in a horizontal industry. Designers often felt like outsiders in their own companies; none of their co-workers really understood what the designers did all day.

Worst of all, there was no unity, no real community of designers. The Internet as we know it was still a few years away. PCB West had just launched; it was the only organized PCB design event, and the only chance for designers to do any networking. What was a designer to do?

Then, as the "Founder of the Designers Council" Gary Ferrari recounts in this month's issue, Dieter Bergman asked him what IPC could do for PCB design. They traveled around the United States, talking to designers and getting a feel for their interest in forming a design organization. Yes, there was plenty of interest. And by 1992, the first DC chapter had formed in Atlanta, followed by dozens more in rapid succession.

> Now there are DC chapters around the U.S. and Canada, as well as Australasian and Southeast Asian chapters. There is no longer any fee to join the council, and the DC counts thousands of members. The local chapters are completely autonomous; some chapter meetings draw huge crowds, and a few chapters are nearly dormant. As the Designers Council enters its 25<sup>th</sup> year, we decided to talk to some people of the who helped make

it all happen. In this issue, we have an interview with IPC's tireless Anne Marie Mulvihill, who gives us a rundown on the DC of today. We also have a discussion with Gary, who takes us all

#### THE DESIGNERS COUNCIL: ELEVATING PCB DESIGN, AND DESIGNERS

the way back to the beginning and shares a little "inside baseball" on the forming of the council.

Design instructor Rick Hartley discusses how he helped start a DC chapter in Ohio, and he lays out the many educational and networking benefits of being involved with your local chapter. San Diego PCB's Mike Creeden talks about his work with the DC, and he explains how the executive board functions as well.

And Zentech's Judy Warner interviewed Freedom CAD's Scott McCurdy, president of the Orange County Designers Council Chapter. The Orange County chapter meetings routinely draw nearly 100 attendees, and Scott was happy to share his "playbook" for starting and sustaining an active DC chapter. I think Scott spends part of each week planning the next DC chapter meeting, but the results speak for themselves.

It's been quite a year. In 2015, we covered a lot of big news. We also said goodbye to some good people, like Gary Smith and Steve Weir. In this issue, don't forget to check out the most popular PCB design articles and news items of 2015.

I hope you have a great holiday. I'll see you in 2016! **PCBDESIGN**

**Andy Shaughnessy** is managing editor of *The PCB Design Magazine*. He has been covering PCB design for 16 years. He can be reached by clicking <u>here</u>.

### Quantum Physics Problem Proved Unsolvable

A mathematical problem underlying fundamental questions in particle physics and quantum physics is provably unsolvable, according to scientists at UCL, Universidad Complutense de Madrid— ICMAT and Technische Universität München. The findings show that even a perfect and complete description of the microscopic properties of a material is not enough to predict its macroscopic behaviour.

The study, published today in Nature, investi-

gated the problem of the 'spectral gap' – the energy needed for a material to transfer from its lowestenergy state to an excited state. When this energy becomes very small (i.e. the 'spectral gap closes'), it becomes possible for the material to transition to a completely different state and the properties of the material can under-

go dramatic changes. For example, when a material at a very low temperature transitions from insulating to superconducting, this dramatic change is the result of its spectral gap closing.

Co-author Dr. Toby Cubitt from UCL Computer Science, said, "Alan Turing is famous for his role in cracking the Enigma code, but amongst mathematicians and computer scientists, he is even more famous for proving that certain mathematical questions are `undecidable' – they are neither true nor false, but are beyond the reach of mathematics.

"What we've shown is that the spectral gap is one of these undecidable problems. This means a general method to determine whether matter

> described by quantum mechanics has a spectral gap, or not, cannot exist."

> The researchers are now seeing whether their findings extend beyond the artificial mathematical models produced by their calculations to more realistic quantum materials that could be realised in the laboratory.

# **IPC DESIGNERS COUNCIL:** Serving PCB Designers for Almost 25 Years

#### by Andy Shaughnessy

You may have seen Anne Marie Mulvihill at the Design Forum during IPC APEX EXPO, rounding up the speakers and PCB designers and basically keeping everyone happy, often with a sarcastic comment or two. As the PCB design program manager for IPC, Anne Marie is in charge of making the train run on time for PCB designers, a task I would compare to herding cats. When I told Anne Marie that we were covering the Designers Council for this issue, she jumped at the chance to help us out.

### **Andy Shaughnessy:** What is the Designers Council's basic mission?

**Anne Marie Mulvihill:** The Designers Council's mission is to provide technical education that connects the design community. This connection makes technology interchange more efficient.

**Shaughnessy:** How does the executive board function? *Mulvihill:* The Designers Council Executive Board is a blue-ribbon group, i.e., open by invitation only. These thought leaders in the design community have all been working at the advanced level for more than 20 years, and are drawn from every market sec-

Anne Marie Mulvihill

tor. They volunteer their time and thoughts to serve as the Steering Committee for IPC Design Programs.

Members of the group meet twice every year in person with IPC staff, and consult informally throughout the year about the direction for IPC programs like Designer Certification, the Designers Council, development of industry standards focused on design, technical courses, and events associated with design.

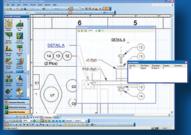

# Solutions to Ensure PCB Manufacturing Success!

# CAM350

Verify and Optimize PCB Designs for Successful Manufacturing.

# BluePrint PCB

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB post processing needs.

# For more information please visit downstreamtech.com or call 800-535-3226.

#### **IPC DESIGNERS COUNCIL: SERVING PCB DESIGNERS FOR ALMOST 25 YEARS**

**Shaughnessy:** What are your membership stats: industry segments, job descriptions, regions of the world, total membership, etc.?

**Mulvihill:** The IPC Designers Council is an international society for all individuals with interest in design. Participants are drawn from all over the world, from every market segment. They hold a variety of job titles; those with "design" or "designer" in them are the majority.

#### Shaughnessy: Do you host any events?

#### Mulvihill: Absolutely.

a. IPC presents the Design Forum every year, within the premier industry event IPC APEX EXPO. This activity features technical presentations from industry thought leaders, in a full-day conference format that allows for both education and networking. The Design Forum 2016 runs on Monday, March 14, 7:30 a.m. – 1:30 p.m. in Las Vegas, at the Convention Center with IPC APEX EXPO.

b. Half-day and full-day technical courses with an emphasis on design are also on the Professional Development slate at IPC APEX EXPO. Courses of particular interest to designers run on March 13–14, Sunday and Monday afternoon. More information about Professional Development courses and the Design Forum can be found at <u>www.ipcapexexpo.org.</u>

c. Designer Certification sessions consist of two days of instruction, plus one day of review with an exam. These sessions are delivered by IPC-licensed training centers, in classrooms all over the world. Successful completion of the courses results in the award of highly respected professional designations: CID (Certified Interconnect Designer) and CID+ (advanced level).

### **Shaughnessy:** What are the top 2-3 benefits you bring your membership?

**Mulvihill:** First would be our design community connections, such as the electronic bulletin board. Designers interested in subscribing should visit <u>our site</u>. We also provide IPC e-mail broadcasts. And the Designers Council chapter meetings allow members to connect with other designers and learn new processes and techniques though periodic "Lunch 'n' Learn" events.

Second would be the discounts DC members can apply to designated IPC industry standards, events, and programs with a focus on design.

### **Shaughnessy:** How much does DC membership cost?

*Mulvihill:* There are no fees associated with participation in the IPC Designers Council.

#### **Shaughnessy:** Tell us about the CID and CID+ certifications. I understand the curriculum has been "updated," if that's the right word.

*Mulvihill:* That is the right word! Course content for both the CID module and the CID+ module have been updated, to help meet design challenges of today's environment. The 2016 editions of CID and CID+ modules are available.

- New content has been added to the course textbook (the Study Guide), slides used for classroom presentation, and the exam. For example: the latest lead-free and other environmental regulatory issues associated with materials.

- Information has been re-organized, for improved flow.

- Exam format has been aligned with today's best practices in testing.

**Shaughnessy:** Is there still a plan to add HDI CID certification?

# When failure is not an option, don't leave your high tech PCBs to chance.

# Have an <u>ACE</u> up your sleeve!

- Specializing in high technology quick turn prototypes, as fast as 24 hrs

- MIL-PRF-55110, MIL-PRF-31032A, AS9100, and ITAR certified

- Leading experts in RF, Hybrid

PTFE/FR4 and Antenna/Microwave

### www.ace-pcb.com

# sales@ace-pcb.com

#### reature interview

#### **IPC DESIGNERS COUNCIL: SERVING PCB DESIGNERS FOR ALMOST 25 YEARS**

**Mulvihill:** Not at this time. When the program was first developed 20+ years ago, the original plan was to expand the offering to a course module on HDI, and one on high-speed design. These topics are introduced in the 2016 edition of CID, and covered in more depth within the 2016 edition of CID+. Publication of a formal certification module takes a long time, due to requirements for multiple reviews. Developments in HDI and high-speed design happen so fast that formal certification module content could be outdated as soon as it is published.

For the most up-to-date information on HDI and other technologies that require advancedlevel design, individuals concerned with design are encouraged to participate in tutorials, courses, and technical conferences. Examples include the professional development courses at IPC APEX EXPO, and the recent IPC Flexible Circuits-HDI Forum.

# **Shaughnessy:** Many of our readers feel standards and certifications should be free to members. How do you address the "free" contingent?

**Mulvihill:** While it would be possible to construct a membership fee that would include all standards and certifications, the fee would be too high because not every employee of every member company would utilize all IPC products and services constantly. It is understandable that this question might be raised, as the incredible amount of time and effort that goes into association "products" like standards and certifications is not always apparent at first glance.

### **Shaughnessy:** What resources (book stores, etc.) are most important to your members?

**Mulvihill:** IPC industry standards are our core offering. We are the only association in this electronics manufacturing industry to provide a platform for development and application of standards for all phases of product realization: design, manufacturing, inspection and test. IPC standards focus on manufacturability and reliability of the finished product, notably the high reliability required of products for the automotive, medical, military and aerospace sectors, as well as products like satellites and servers.

### **Shaughnessy:** How do you satisfy members' need for technical information?

**Mulvihill:** Our mission is to provide industry standards and technical education, including training and certification, education with a design focus.

**Shaughnessy:** Highlight some of the Designers Council's success stories.

Intercept's complete design flow gives you the power to keep moving, full speed ahead. Use Mozaix for flexible schematic capture and Pantheon f or a dvanced, i ntuitive PCB/Hybrid/RF design to move quickly and seamlessly from concept to manufacturing. Our 30+ import transla tors make it easier than ever to switch tools. Let Pantheon and Moz aix drive your next innovation.

PANTHEON ADVANCED PCB, HYBRID, RF LAYOUT MOZAIX NEXT GENERATION SCHEMATIC CAPTURE REUSE BLOCK TECHNOLOGY MULTI-BOARD & PANEL ARRAYS LAYOUT-DRIVEN DESIGN & PROTOTYPING SIMULATION & ANALYSIS INTERFACES DESIGN AUTOMATION DFM & ARTWORK VERIFICATION HIGH SPEED DESIGN ARTWORK PANELIZATION AUTOMATIC DRAWING CREATION 30+ TRANSLATORS

www.intercept.com

30+ Years of EDA Software Solutions

#### **IPC DESIGNERS COUNCIL: SERVING PCB DESIGNERS FOR ALMOST 25 YEARS**

**Mulvihill:** Veteran designers tell us that IPC Designer Certification is the best educational program for design practices in the industry. The CID and CID+ are professional designations respected throughout the industry, specified for major projects and utilized by major corporations for selection and promotion.

## **Shaughnessy:** Do you have partnerships with other industry organizations?

*Mulvihill:* IPC works on projects in partnership with other industry organizations, notably:

- CALCE (Center for Advanced Lifecycle Engineering—University of Maryland)

- SMTA (Surface Mount Technology Association)

- EIPC (European Institute of Printed Circuits)

- FED (Fachverband für Design, Leiterplatten- und Elektronikfertigung association for PCB design and manufacturing)

- AIA (Aerospace Industries Association)

- NAM (National Association of Manufacturers)

- WECC

- SEMI

- DDMII

**Shaughnessy:** Does the DC help members deal with government agencies?

**Mulvihill:** No. The IPC Government Relations team handles issues associated with environmental and governmental regulations that affect the electronics industries.

#### **Shaughnessy:** What are your most successful programs and why?

**Mulvihill:** The IPC 2581-Consortium was formed nearly 10 years ago. Persuading all of the major CAD software vendors to put aside their differences and bringing them to the table for good of the industry was a major effort. Drawing in OEM users to provide input and consent to utilize the standard for beta-testing was the next step. The next phase will be to apply the IPC-2581 to a larger number of facilities, using a variety of CAD software design and assembly tools.

This industry standard consists of generic protocols for consistent capturing and transmission of design data through all phases of product manufacture—the Holy Grail. This is a great achievement, culminating in a quiet revolution that could result in quality and efficiency improvements throughout the entire electronics industry.

# **Shaughnessy:** Why should someone join the DC? It sounds like there are no risks, only rewards.

**Mulvihill:** Individuals in the electronics industry should have an awareness of the importance of design. Up to 75% of a product's cost and performance can be attributed to design.

# **Shaughnessy:** Is there anything else you would like to share?

**Mulvihill:** For more information on the IPC Designers Council, please contact Kris Roberson, manager, Certification Development at 1-847-597-2846 or KrisRoberson@ ipc.org.

**Shaughnessy:** Thanks for your time. See you at APEX!

Mulvihill: Thank you. PCBDESIGN

# Engineering And Providing Balanced Interconnect Solutions

#### Flexible Printed Circuits • Rigid Flex • Wire Harnesses • Complete Assemblies

Our products and services are specifically designed to empower our customers to produce a product with superior performance and quality, as well as lower design, assembly, and system installation costs.

#### Partnering With Your Engineering Team To Deliver The Best Solution

...connecting technology

Miraco, Inc. • 102 Maple Street, Manchester, NH 03103 • miracoinc.com 603-665-9449 • Fax: 603-665-9459

by Judy Warner ZENTECH MANUFACTURING

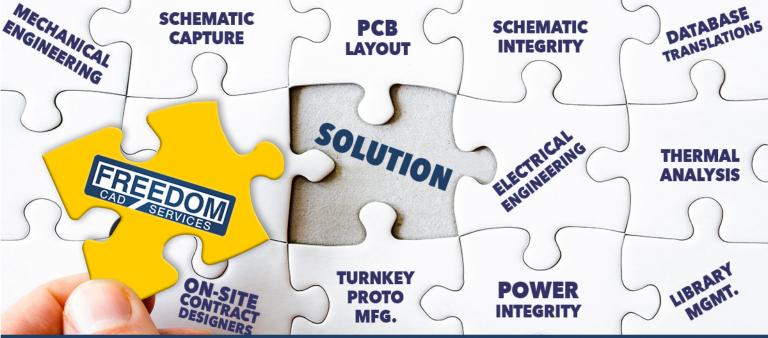

As a Southern California native and an industry veteran, the name Scott McCurdy is a familiar one for me. Scott has been in the electronics industry for 40+ years. Thirty-two of those years were spent building and running McCurdy Circuits, a successful PCB fabrication facility in Orange County. These days, Scott is focused on the design side of things as the director of sales and marketing for Freedom CAD Services, the largest independent design bureau in the nation.

In his not-so-sparetime, he is also the president of the largest chapter of the IPC Designers Council in the country. Despite the fact that I've known about Scott since the mid-1980s, we only just met within the last year. Shortly after meeting Scott, he began encouraging me

Scott McCurdy

to attend the local Designers Council meetings that he hosts approximately 3–4 times per year in Irvine, California. Thankfully, although I stood him up for a couple of meetings, he persisted (a little friendly harassment) and eventually, pushing skepticism aside, I got around to finally experiencing what he was so enthused about.

#### From Reluctance to Raving Fan

When I finally made that first meeting last March, I arrived late. As I tried to slink in the door unnoticed, I awkwardly realized there wasn't an empty seat in the house--until one magically appeared in the back of the room. I was awestruck by the attendance of 77 otherwise busy designers and electronics professionals who filled the room. Tom Hausherr of PCB Libraries was the featured speaker for my first meeting.

The next meeting was held in June at a member location, Broadcom. That meeting featured two speakers: Matt Isaacs, technical director of Broadcom and Julie Ellis, a field application engineer with TTM; nearly 100 people attended. My third meeting, which took place at Harvard Park Community Center in Irvine on Novem-

# WE HAVE ALL THE PIECES TO SOLVE YOUR ELECTRONIC DESIGN CHALLENGES

# World-Class PCB Design and Engineering Solutions

Trust our experienced team of Electrical Engineers to take your ideas and specifications and accurately engineer your product from concept to prototype assemblies. In fact, we love a good challenge, so *bring it on*!

- Complete Engineering Project Management

- Circuit / Schematic Design & Analysis

- Power / Voltage Drop Analysis

- Component Analysis / Evaluation

- Signal Integrity Simulation & Analysis

- Mechanical Engineering

- PCB Layout Team Available 24/7

- Largest Privately Owned, Independent Service Provider in the USA

#### **REQUEST A QUOTE**

cādence

Altıum

**ANSYS**

Freedom CAD Services, Inc. HQ, Nashua, NH (603) 864-1300

Sales: • (714) 490-7600 Tustin, CA

- (408) 529-0563 San Jose, CA

- (603) 864-1342 Windermere, FL

Menior

pads

dal ools

PCB DESIGN • ELECTRICAL ENGINEERING • MECHANCIAL DESIGN • SCHEMATIC CAPTURE • TURNKEY MFG.

#### **MCCURDY: HOW TO BUILD A SUCCESSFUL IPC DESIGNERS COUNCIL CHAPTER**

ber 18, broke the attendance record for their home meeting location, topping out at 89 attendees. Chris Heard of CSH Consulting gave a rich and granular talk about signal integrity and power issues relative to routing guidelines and layout features. At these meetings, I witnessed designers being granted access to a very high level of educational and networking opportunities that deeply enriched and inspired them to grow as professionals. In some cases, it has inspired them to even further their formal education or certifications that helps them compete in a fierce global marketplace. In a matter months, I had been transformed from skeptic to a raving fan!

#### On Becoming the Accidental Chapter President

After the last meeting, I had the opportunity to talk at length with Scott about his 13-year tenure as the Orange County chapter president. It's clear that he is absolutely passionate about the value of the Designers Council and the immense educational value and resources it can deliver to the industry in a convenient, low cost and regional context. In our time together, he openly shared his "playbook" on how to build and run a successful Designer's Council chapter, which he is eager share with others who may be interested in launching a local chapter would like to emulate his success. The excitement and generosity he showed instantly compelled me to pass on both his story and his recipe for success.

When Scott made his transition from PCB fabrication to a PCB layout focus, about 13 years ago, he accepted an invitation to attend our local IPC Designer's Council. Shortly after, he was recruited to serve on the group's steering committee. At that time, 20–25 people were regularly attending the meetings. Within 3–4 months, the chapter's president made an unforeseen move to Arizona and he asked Scott to take his place.

Since that time more than 12 years ago, he has continually served as the chapter's president and has grown it into the nation's largest chapter. He is quick to give credit to the tremendous support he has had from Terri Kleekamp of Mentor Graphics, and Kathy Palumbo of Production Analysis and Learning Services, who have faithfully supported the chapter since before he arrived. They have both been an invaluable help as chapter secretary and treasurer, respectively.

Although this role came along unexpectedly, Scott immediately rolled up his sleeves and went to work to raise awareness of the meetings to our local PCB design and electronics community. He began by e-mailing invitations and making face-to-face appointments with design professionals and personally inviting people to attend and participate in the local events. The meetings were held at Mentor Graphics 4–5 times per year. In short, Scott built the local Orange County chapter by building relationships one at a time through some hard work and his signature dogged persistence.

Meeting attendance doubled almost immediately, causing them to eventually outgrow the Mentor Graphics office and move to its current location. With the support of Terri and Kathy, attendance grew, in fits and starts, until it became what it is today.

#### **McCurdy's Playbook for Success**

For those of you who may have considered starting a local chapter, or who currently run a Designers Council chapter, here is some basic information from McCurdy's playbook, which he has been improving for nearly 13 years.

First of all, IPC Designers Council membership is free, and you can register <u>here</u>. To find out more about starting a local chapter contact

#### MCCURDY: HOW TO BUILD A SUCCESSFUL IPC DESIGNERS COUNCIL CHAPTER

IPC by clicking <u>here</u>. Kris Roberson is the point of contact for Designers Council chapters at IPC.

The essentials of running a good meeting consist of the following:

- Although some chapters hold evening meetings, Scott has found that holding the "Lunch and Learn" events from11:30 a.m. – 1:30 p.m. works well. This makes little impact on a busy professional's working hours, and does not infringe on personal or family time in the evenings. Traffic patterns in busy cities are also lighter in that time slot. Most companies will support time away from the office when it is the equivalent to a long lunch to serve continuing education.

- Find relevant speakers who are valuable to the PCB design community. Choose one speaker to talk for 80 minutes, or two speakers to talk for 40 minutes each.

- Meeting times run two hours; 80 minutes are reserved for speakers. Lunch and announcements account for another 30 minutes, and the remainder is set aside for questions, raffle and closing.

- Always make name tags that are easily readable and that also include the company name for ease of networking.

- Provide box lunches from a local sandwich shop, and charge approximately \$10 at the door to help cover costs of facility and food/drinks.

- Proactively network between and during meetings to build rapport and keep a growing database for the chapter.

- Occasionally take on-site field trips to provide learning opportunities and to raise awareness of member companies (i.e., PCB fabrication facilities, design bureaus, OEMs, or contract manufacturers).

- Get member companies to sponsor some simple prizes to raffle at the end of the meeting.

- The president should greet members as they arrive and as they depart, and thank them for attending.

- Get help from a few volunteers to help shoulder the work involved. It takes a team to grow a chapter!

- If you can, get a member company to open up a meeting space at no charge to help keep costs to a minimum.

- Include opening slides that include:

- A greeting and welcome

- IPC information and website link

- Information and links for industry magazines/news sources

- Share information regarding upcoming local events, such as tradeshows

- Open the floor to ask if anyone is hiring or looking for a design job in order to make potential matches

- Encourage feedback and ask attendees about topics and speakers they would like to hear from.

- Give handouts to gather contact information about the attendees, and add new info to the database.

- Provide the website links mentioned in the opening slides in written form.

- Ask the speakers to provide the slides from their talk, removing any proprietary information, and forward to the attendees via email or a customized website.

#### Give with Purpose: Educate, Network, Inspire

While Scott McCurdy's "recipe" is a fairly simple one, there is one intangible quality that I observed that appears to have contributed greatly to his success with the Orange County

#### MCCURDY: HOW TO BUILD A SUCCESSFUL IPC DESIGNERS COUNCIL CHAPTER

Chapter: He's a giver. Scott doesn't give to get something in return—he gives for the joy of contributing to our industry. And he has surrounded himself with like-minded contributors like Terri Kleekamp, Kathy Palumbo and others. He enjoys providing designers with resources that will educate, inspire and allow them to network with their peers. Subsequently, designers become better at what they do, which empowers them to compete well globally. Generosity and altruism are at the heart of Scott's and his team's success.

If you want to follow in Scott's shoes and set up your own Designers Council chapter, be a purposeful giver. Beyond that, carve out some time to build relationships in order to support your efforts and to grow meeting attendance. No matter how much we rely on our electronic devices to inform and connect us, nothing compares to the power and value of meaningful face time. Scott's playbook, and his support of local design professionals, are keys to his chapter's success. **PCBDESIGN**

**Judy Warner** is director of business development for the Western Region and RF/microwave markets for Zentech Manufacturing.

### Nanostructured Metal Coatings Let the Light through for Electronic Devices

Light and electricity dance a complicated tango in devices like LEDs, solar cells and sensors. A new anti-reflection coating developed by engineers at the University of Illinois at Urbana Champaign, in collaboration with researchers at the University of Massachusetts at Lowell, lets light through without hampering the flow of electricity, a step that could increase efficiency in such devices.

The researchers, led by U. of I. electrical and computer engineering professor Daniel Wasserman, published their findings in the journal Advanced Materials.

At the interface between two materials, such as a semiconductor and air, some light is always reflected, Wasserman said. This limits the efficiency of optoelectronic devices. If light is emitted in a semiconductor, some fraction of this light will never escape the semiconductor material. Alternatively, for a sensor or solar cell, some fraction of light will never make it to the detector to be collected and turned into an electrical signal. Researchers use a model called Fresnel's equations to describe the reflection and transmission at the interface between two materials. "It has been long known that structuring the surface of a material can increase light transmission," said study co-author Viktor Podolskiy, a professor at the University of Massachusetts at Lowell. "Among such structures, one of the more interesting is similar to structures found in nature, and is referred to as a 'moth-eye' pattern: tiny nanopillars which can 'beat' the Fresnel equations at certain wavelengths and angles."

Although such patterned surfaces aid in light transmission, they hinder electrical transmission, creating a barrier to the underlying electrical material.

The researchers demonstrated that their technique, which results in metal covering roughly half of the surface, can transmit about 90 percent of light to or from the surface.

# Delivering the highest quality standard for Aerospace and Defense

### Ventec Europe Accredited to AS9100 Revision C

www.ventec-europe.com

We are proud to announce that the quality management system at our Leamington Spa, UK, headquarters is now fully accredited to AS9100 Revision C (the two facilities of our parent company, Ventec Electronics Suzhou Co Ltd, have been fully AS9100C certified since 2012).

AS9100 is the quality management standard specifically written for the aerospace and defence industry, to satisfy authorities such as the Federal Aviation Administration, ensuring quality and safety in the "high risk" aerospace industry.

www.ventec-usa.com

www.venteclaminates.com

#### reature interview

# **Cipc** Designers Council Viewpoint: Gary Ferrari

When we started putting together our coverage of the Designers Council, we knew we'd have to get the real scoop from Gary Ferrari. He's been helping to raise the status of the PCB designer for decades. As co-founder and longtime executive director of the Designers Council, as well as an IPC Master Instructor, Gary has dedicated a big part of his career to PCB design. After decades of service, he was inducted into the IPC Hall of Fame at IPC APEX EXPO this year.

I caught up with Gary and asked him to fill us in on the creation of the Designers Council, and some of the changes he's seen in the organization in the last 24 years.

#### **Andy Shaughnessy:** You're often referred to as the "Founder of the Designers Council." How did you get involved and who else helped get the DC started?

**Gary Ferrari:** As you know, Dieter Bergman and I worked together on many of the standards that affect designers. We also did several designer-oriented workshops. One day, Dieter asked me what more IPC could do for the design community. My answer was very simple: "Mechanical engineers have the ASME, electrical engineers have IEEE, and the designers have sore eyes from staring at their monitors. What we need is a society

for board designers, and anyone with a vested interest in board design."

In 1991, we hit the road and traveled throughout the U.S. to introduce a new design standard. It also gave us an opportunity to poll the attendees to hear their comments on whether

Gary Ferrari

an IPC Designers Council was a good idea. We also asked them what they felt its charter should be. The primary feedback was designer education, a forum to discuss common interests, and network building. In summary, they liked the idea of a designer society.

However, an issue was IPC's membership structure. Their membership is company-based, whereas a society is generally individual-based, similar to SMTA. After consulting with IPC's legal counsel, we were able to structure the Designers Council as a chapter-based entity, thus allowing for individual membership.

**Shaughnessy:** Where was the first official DC meeting held, and when?

# WE ARE THE NEW EASY BUTTON FOR PCB APPLICATIONS

At American Standard Circuits, we want every facet of your PCB manufacturing experience to be uncomplicated. From problem solving and technical expertise to unmatched customer service, we make every step easy until your job is complete.

Digital RF/Microwave Flex Metal Clad RoHS

American Standard Circuits Creative Innovations In Flex, Digital & Microwave Circuits

www.asc-i.com

#### **IPC DESIGNERS COUNCIL VIEWPOINT: GARY FERRARI**

*Ferrari:* Its official birth was in 1992. Dieter and I were making the rounds doing design-related workshops at that time, and spreading the word. Chapters started forming at a tremendous rate. We were up to 29 chapters within several months.

What is interesting to note is that a group of Atlanta designers

had been meeting together for about a year under the leadership of Fred Pescitelli, at Phoenix Designs. They met to learn from each other, learn about new technologies, etc. Sounds familiar doesn't it? They listened to what we offered, voted, and Atlanta became the first official chapter of the IPC Designers Council.

No matter where I traveled, the local designers basically said the same things. One that comes to mind was in Atlanta. One of the wellknown designers, when asked the how he felt designers were viewed, indicated that the attitude was that designers were "pond scum." We can certainly laugh at his colorful description, but I received similar answers no matter where I traveled.

# **Shaughnessy:** What are the biggest changes you've seen at the DC in the past 24 years?

**Ferrari:** There are fewer registered chapters in the U.S., whereas we have seen a much larger growth internationally. However, we have recently witnessed a few new chapters starting up. We are also seeing more and more engineers taking the certification courses. I recently taught a class that consisted of over 90% engineers. In addition, we see a growth of new, younger designers taking the courses.

Two reasons may be attributed to these observations. The first is that technology has become more sophisticated, and engineers are being asked to move further into the layout end of the development cycle. The second is that the average age of the designer keeps climbing up, resulting in much larger numbers getting ready for retirement. Companies are finally waking up to the fact that they will be losing a significant part of their product development team, better known as the PCB designer.

**Shaughnessy:** What do you think are the biggest benefits that the Designers Council offers designers, and the industry?

**Ferrari:** This answer is three-fold. The first is exposure to industry standards, which includes many important processes that are af-

fected by design. Let's face it, with today's technologies, the designer cannot ignore what his design may do to the fabrication, assembly and test segments.

The second is obtaining a professional credential that has international recognition.

The third is building a network of experts that one may call on when faced with a new or difficult design issue.

#### Shaughnessy: What's exciting about the DC today?

**Ferrari:** In the certification program, we see many new design challenges facing the designer. These are worldwide challenges that create new horizons. In other words, I see plenty of growth for those who are coming into the field, as well as those who have been around for a while. As chairman for several IPC design-related standards, I look for a path into the standards for these challenges, and ultimately into the designer certification courses. For me, I have to mention all the designers I have met and helped in one way or another. To see them grow and be successful is amazing.

#### **Shaughnessy:** Why should someone consider joining the DC?

**Ferrari:** Technology does not wait for designers to catch up. It moves forward and designers need a venue that enables them to keep up with these technology changes through education and networking. Being involved in a local Designers Council chapter may provide the catalyst for their employers to allow them to attend various conferences and help expand their knowledge.

#### Shaughnessy: Thanks, Gary.

Ferrari: Thank you. PCBDESIGN

# Pulsonix

Advanced Schematic Capture and PCB Design Software

# A refreshing approach to simplifying Schematic Capture and PCB Design

- Import filters for all major tools (designs and libraries)

- Very easy to learn and use

- 5-Star Service and Support

Download a Free Trial

info@pulsonix.com www.pulsonix.com

Designers Council Viewpoint: Rick Hartley

#### by Andy Shaughnessy

Rick Hartley has been in involved in PCB design and design education for decades, so it's no surprise that he started working with the IPC Designers Council early on. Now retired from his day job at L-3, Rick still teaches PCB design and shows no sign of slowing down. I asked him to discuss his work with the Designers Council, and what the group means to the design community.

**Rick Hartley**

# **Andy Shaughnessy:** How and when did you get involved in the Designers Council?

**Rick Hartley:** I first learned about the Designers Council at an IPC conference in the early 1990s. Shortly afterward, I was contacted by another central Ohio designer, Candice Antrett, of Battelle Research Institute. Candice was also interested in the DC and suggested we collectively start a chapter. Pete Waddell had Printed Circuit Design magazine do a mailing for us to help get the word out, and we have always been grateful for that generous act. We held our first meeting at Battelle, and were off and running. Our membership area was mainly Columbus, Dayton and Cincinnati.

# **Shaughnessy:** What are the some of the most important benefits that the Designers Council offers designers, and the industry?

**Hartley:** For those chapters that are still going strong, the benefits are massive. There is NO formal education in PCB design. For the most part, colleges do not teach the profession. Some colleges barely even mention the existence of PC boards, much less tell their students anything meaningful. IPC and the active DC chapters are doing a wonderful job of training the industry

# Quality PCBs from the established industry leader

With over 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits<sup>®</sup> is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

### Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for over 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

#### **IPC DESIGNERS COUNCIL VIEWPOINT: RICK HARTLEY**

about the many issues we need to understand; I don't mean just designing to make boards function, but incredibly important issues like DFX (i.e., design for fabrication, design for assembly and design for testability). For people who do not live in the area of an active chapter, there is the IPC APEX EXPO conference and other wonderful educational resources, such as PCB West Design Conference and online webinars from multiple sources, including IPC.

#### Shaughnessy: What's exciting about the DC today?

**Hartley:** All the items mentioned earlier. And, of course, there is the CID (Certified Interconnect Designer) and CID+ (Advanced) training and certification. This can be a very valuable asset to designers and EEs. One of the greatest benefits I derived from chapter membership was networking. I could write a book on the value of networking with others in your profession. Those folks lucky enough to still have a local chapter and those who network at conferences know exactly what I mean.

#### **Shaughnessy:** We've covered a few DC meetings and "lunch and learns" lately, and they've had good attendance. Are the local chapters becoming more active, like they were a few years ago?

*Hartley:* The chapters that are active are very active. A great example is the Orange County chapter in Southern California. These guys are

doing a fantastic job of training and educating designers, fabricators and assembly people. I cannot say enough about the great work that Scott McCurdy and the other officers of the Orange County chapter are doing.

Unfortunately, in recent years, a number of other chapters have become less active, the Greater Ohio chapter included. We did not lose interest; we were mainly a self-education group and, after 14 years, simply ran out of things to tell each other. We were fortunate to have a fair number of people with something valuable to say, and we did it for 14 years. We have been talking lately about possibly rekindling the flames. It's been just long enough that we believe we have new things we can teach each other. Anyone who wants to know more about the Designers Council can find information on IPC's website. If vou want to get more involved in education for the industry, don't just join the DC; start a local chapter and help to educate others.

# **Shaughnessy:** You're the vice chair for the DC. Where is the group headed in the next few years?

**Hartley:** We are constantly updating and improving the CID and CID+ training. These are complex training programs and they are everdeveloping. Also, there has been talk for years about Focus Modules that would be used to train people in specific disciplines related to CID and CID+ (HDI, EMI, etc.). We continue to discuss these possibilities. We are always looking for ways to educate the industry.

#### **Shaughnessy:** In addition to the benefits you mentioned earlier, why else should someone consider joining the DC?

*Hartley:* Education and networking! When I decided 23 years ago to teach at our local chapter meetings, I had no clue how much I would learn in the process of developing training material to educate others. If your goal is to better yourself, don't just go to conferences. Get involved!

#### Shaughnessy: Thanks, Rick.

Hartley: Thank you, Andy. PCBDESIGN

# High Reliabiliy Material for High Speed Applications

(Click on a product logo for more info!)

# Thin Core: S7439/Prepreg: S7439B

Low Loss and High Reliability Material for Complicated PWB Design

# Synamic 6

# Synamic 6N

# Thin Core:S7335/Prepreg:S7335B

Ultra Low Loss and High Reliability Material for Complicated PWB Design 25+Gbps Transmission Applications

www.paramount-usa.com

reature interview

#### by Andy Shaughnessy

When covering the IPC Designers Council, one quickly learns that it's the volunteers who make the train run on time. San Diego PCB CEO Mike Creeden, CID+, is one such volunteer, and as a member of the Designers Council's Executive Board, he was a must-have for this issue. I tracked him down and asked him to give us a rundown of his involvement with the DC, and to explain why designers might want to get involved with their local DC chapters.

### **Andy Shaughnessy:** How and when did you get involved in the Designers Council?

**Mike Creeden:** Around1993, I was presented by a fellow designer an invitation to attend a new meeting called the "IPC Designers Council," which was being held at Qualcomm. I had known of IPC for most of my career of 17 years, but I did not know anything about a Designers Council. So, being curious by nature, I attended this meeting and immediately saw several fellow designers I was well acquainted with, and then I met several new people whom I still see to this day. There was some good food and it was an event outside of work, so I really started to enjoy the meeting.

What came next was profound. I was exposed to IPC standards and the value they brought to my designs, my company and ultimately my career! I saw that the charter of these meeting was to bring this education out to the designer in the workplace as a form of education. So being the naïve person I am, I asked, "What are we doing to get this message out there to those that don't know about this Designers Council chapter?" The response was simple. "What do you think we should do and how would you like to go about it?" I was nominated as the Education board member and had the privilege to serve for several years.

# **Shaughnessy:** What do you think are the most important benefits that the Designers Council offers designers and the industry?

**Creeden:** The Designers Council is a multifaceted organization and as such has been several different things to me over the years. I assume this must be true for other people as well. The primary benefit that the DC brings is improve-

# How can you find the best PCB Partner? We can tell you. We wrote the book on it.

Since 1985, U.S. Circuit has been a premier supplier of both commercial and military Printed Circuit Boards in the United States. We know what it takes to be a good PCB partner. And we want to share what we've learned with you.

Choosing a PCB partner isn't hard—if you know what to look for. We've broken it down into "The 5 Commandments" and you can download it for free.

We are proud to be the Circuit Board Manufacturer of more than 400 growing companies, and even prouder to be a good partner for all our customers!

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

#### Click to Download

#### **IPC DESIGNERS COUNCIL VIEWPOINT: MIKE CREEDEN**

Mike Creeden

ments to the products in our industry. It does so by way of improving the knowledge base of each designer who attends and participates. The products we design become more reliable by applying the proven standards as determined by the experts in the industry, from a cross-section of the marketplace.

When we as designers bring improvements to our company, we're recognized by our peers and by our employers. We may not always be rewarded, but as your value goes up, maybe it's time to find a company that would recognize and reward your value. Another aspect that I mentioned earlier is the opportunity to network with others in your profession. This can be in the form of meeting old friends or making new friends. Maybe it is a time when you can learn some helpful methods to deal with technical issues or a professional response to something that was occurring in your workplace. Often, business connections and business deals can occur based on the contacts that you make through the Designers Council. When someone sees you attending, participating, and contributing in a public forum, they may become interested in services you offer, your expertise, and your ability to use it well.

**Shaughnessy:** What's exciting about the DC today?

**Creeden:** What I find very exciting about the Designers Council is the wealth of knowledge that is presented and exchanged by the members of the group, not to mention the guest speakers that present at the chapter meetings. Our chapter has been known to take field trips to various manufacturing companies; they often provide an educational tour of their facilities and explain the process flow. The fabricators teach us how to avoid common mistakes and better understand the process. With the rapid pace that technology is moving it is imperative to stay current with the industry trends and technical requirements.

### **Shaughnessy:** You're on the executive board for the DC. How does the board operate?

**Creeden:** The executive board is a group of individuals who understand the value of service. Almost everyone participates at the expense of personal time and resources. Their commitment to the improvement of our industry is humbling to watch at times. They do not serve for the reward or prestige of office. They seem to serve for the betterment of their industry and the growth of knowledge.

The board meetings themselves are often very casual events that include food, a lot of good jokes, and several intriguing stories. But when it comes down to business, it is professional and orderly. A few officers are voted into positions for a term. The executive board defines and supports the Designer Certification Program (CID and CID+) as owned by IPC and facilitated by companies like EPTAC. The board members are typically significant contributors to IPC efforts and industry-related technical training sessions held across the country each year.

All local Designers Council chapters are autonomous. Groups have a general charter as defined by the executive board and posted on IPC's <u>website</u>. Each local chapter tends to take on its own identity based on the participation of each group.

Shaughnessy: Mike, thanks for your time.

Creeden: Thank you. PCBDESIGN

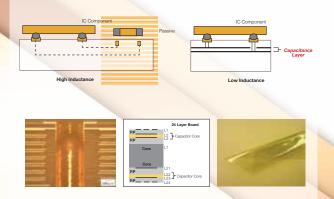

# THE SMART SOLUTION TO IMPROVE SYSTEM PERFORMANCE

# FARADFLEX ULTRA THIN MATERIALS FOR HIGHER PERFORMANCE PCBS

Faradflex is a high performance, ultra-thin laminate or resin coated copper material designed as an integral part of the PCB, module or chip package.

# FaradFlex<sup>®</sup> Improves System Performance, Price, Quality, and Reliability by:

- Reducing PCB size and/ or thickness

- Utilizing VSP Copper to provide the lowest loss signal for high speed designs

- Increasing functionality

- Improving power distribution (power integrity)

- Reducing the number of SMT Discrete Caps, Traces, Vias, Pads

- Eliminating hundreds (thousands) of SMT and etched and drilled features sites for possible failure on each PCB

For a free sample contact us at: sales@oakmitsui.com or call us at 503-313-1905

EMBEDDED CAPACITANCE

For more information, visit www.faradflex.com

# 2015's Most-Read

#### **Engineer Steve Weir Has Passed Away**

Steve was a power and signal integrity guru with a variety of patents to his name. A fixture of DesignCon and a constant presence on the SI-List signal integrity forum, Steve wrote over a dozen papers on pow-

er integrity. He also had a crazy, irreverent sense of humor that you don't find among most engineers. He will be missed.

#### Mentor Graphics Launches New HyperLynx SI/PI Product

Mentor Graphics Corporation has announced its newest version of the HyperLynx Signal Integrity/Power Integrity (SI/ PI) tool for high-speed printed

circuit board (PCB) designs. HyperLynx addresses high-speed systems design problems throughout the design flow—starting at the earliest architectural stages through post-layout verification.

#### EMA and Arena Solutions Form Strategic Alliance

The OrCAD and Arena integration provides a number of benefits for organizations using both systems. Components from the enterprise PLM system are available directly within the OrCAD Capture CIS design environment making search, selection, and placement very simple. Parts listed as obsolete in the PLM system can be easily identified and swapped out in an OrCAD design.

#### Sunstone Circuits Chooses InSight PCB Software for Pre-CAM and Sales

Sunstone Circuits has purchased Orbotech's InSight PCB pre-sales and pre-engineering software. InSight PCB is a web-based tool for managing and assessing incoming customer PCB data for salespeople and

engineers who are not CAM experts. From automatically retrieving comprehensive product information to generating precise summary reports, InSight PCB empowers sales and engineering people to work more independently, efficiently and profitably.

#### Improving PCB Design with Advanced Circuits' PCB Artist

Advanced Circuits' free PCB layout software PCB Artist has become a favorite not only with engineering students but also advanced engineers due to its easy sche-

matic-to-PCB layout, Gerber format, autorouter, and extensive library of over 500,000 parts.

#### Pulsonix 8.5 Build 5902 is Released

WestDev Ltd. has released the latest version of Pulsonix 8.5, Build 5902. This maintenance update is issued as part of our on-going process of product improvement and response to customer feedback. In

addition to bug fixes, the latest release contains several additions to the Report Maker function.

#### Exception PCB Solutions Design Service Boosts CID+ Qualifications

Heading up the design service is Neil Day, who has completed the IPC PCB Designer Certification Program and became qualified as an Advanced Certified Interconnect Designer (CID+). In addition, Tech-

nical Support Manager Paul Beech has completed the IPC CID training course and attained CID certification.

#### Polar Instruments Launches New Language Versions of The Speedstack PCB Layer Stackup Design System

Polar Instruments has launched new language versions of Speedstack, the industry's best-selling PCB layer stackup design system. In addition to English, Speedstack is now available in German, Japa-

nese, simplified Chinese and traditional Chinese versions. Speedstack allows PCB fabricators to finetune the stackup design by assessing the impact of different PCB materials on cost, performance and manufacturing yield.

### cited 53% Limited time to develop PCBs Need to cited 32% support better collaboration cited Manufacturing 21% mm delays due to data inconsistencies 19% cited **Better predictability** of design cost

## What Are Your PCB Data Management Challenges?

EMA Design Automation commissioned independent research firm The Aberdeen Group<sup>®</sup> to conduct a study on current trends and challenges with regards to PCB data management.

Download the full research paper to learn how best in class companies are taking control of their PCB design data and turning data management into a competitive advantage.

Download Report >

column

**BEYOND DESIGN**

## Plane Crazy, Part 1

#### by Barry Olney

IN-CIRCUIT DESIGN PTY LTD AUSTRALIA

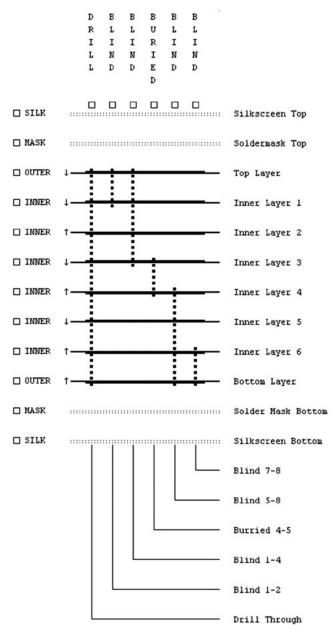

A high-speed digital power distribution network (PDN) must provide a low inductance, low impedance path between all ICs on the PCB that need to communicate. In order to reduce the inductance, we must also minimize the loop area enclosed by the current flow. Obviously, the most practical way to achieve this is to use power and ground planes in a multilayer stackup. In this two-part column, I will look at the alternatives to planes, why planes are used for high-speed design and the best combination for your application.

Back in the mid-eighties, when I worked at the University of Western Australia, one of my duties was to fix the departmental mainframe: the dreaded DEC PDP-11/40. When it broke down, it was a two-week sentence to solitary

Figure 1: Unibus board (courtesy of DEC).

confinement in the frigid computer room. This monster machine had card after card with rows of TTL logic chips. Figure 1 illustrates a typical Unibus board. It had 8K, 16-bit word core memory, which I believe could be expanded to 80K if the need ever arose. The core had a 400ns access time, which means the system clock would have been a blazing 2.5MHz.

I always used the "divide and conquer" methodology. First, eliminate the power supplies then start dividing the system in half, then half again until the fault was localized within a small circuit. But, as it took about half an hour to reboot, with a specific sequence of octal latches, it was a very time consuming process. Plus, there were always numerous engineering students banging on the window, to the terminal room, enquiring when the "mother" might be fixed so they could complete their assignments.

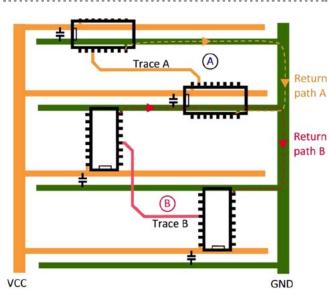

The boards were double-sided and used a power finger, type A or B layout configuration on the top side of the board, as shown in Figure 2. The bottom side could then be used entirely

Figure 2: Power finger configuration.

## We deliver Advanced PCB Solutions!

## Landless Via Technology

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

CLICK TO LEARN MORE

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

## Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

CLICK TO LEARN MORE

## Impedance Tolerance <5%!

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

CLICK TO LEARN MORE

CANDOR INDUSTRIES, INC. ADVANCED PCB SOLUTIONS

www.candorind.com | sales@candorind.com | (416) 736-6306

#### PLANE CRAZY, PART 1

for routing. This provided some mutual inductive coupling between the wide power and ground traces and saved on board area. However, it meant that the return current had to flow all the way around the board perimeter, creating a large loop area. Fortunately, the PDP-11/40 was manufactured way before the era of FCC-mandated radiation guidelines. Needless to say, this is not a good supply configuration for high-speed design. Don't try this at home!

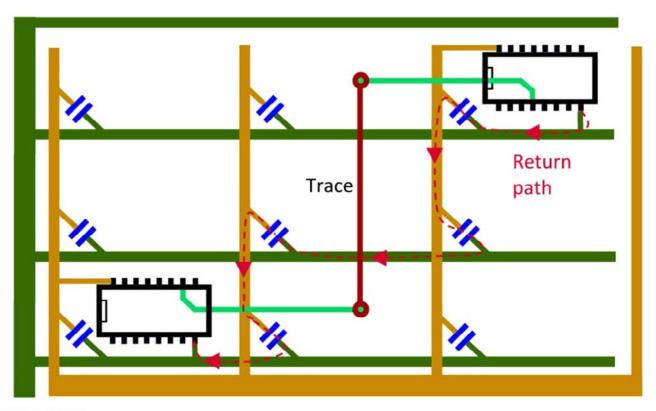

The power and ground grid configuration of Figure 3 also saves on board area, but at the expense of increased mutual inductance. In this case, the ground (GND) traces are horizontal on the bottom of the board, while the power (VCC) traces are vertical on the top side. Connecting the two supplies, at every intersection, with a decoupling capacitor forms a cross-hatch pattern. Current returns equally well, to its source, along either the ground or power traces. The down-side here is that the capacitors used should be of particularly good quality (low ESL) as the return current must traverse several capacitors to return to the source. If you are limited to a double sided board, then this is the best approach for providing power to the network of chips. But, solid copper planes, in a multilayer configuration, are of course a much, much better solution for high-speed design.

Although it is true that a plane has significantly less inductance than a trace, plane inductance is not negligible. The mechanism by which a plane reduces the inductance is by allowing the current to spread out, effectively creating numerous parallel paths. But at high speeds, return currents flow the path of least inductance which tends to direct the current directly below the signal trace.

Also, due to skin effect, high-frequency currents cannot penetrate a plane, and therefore, all currents in conductors are surface currents. This effect will begin to occur at frequencies above 30 MHz for 1 oz. copper layers in a PCB. Therefore, at high frequencies, a plane in a PCB is really

#### GND VCC

Figure 3: Power and ground grid configuration.

two conductors—not one conductor. There will be a current on the top surface of the plane, and there can be a different current or no current at

all on the bottom surface of the plane.

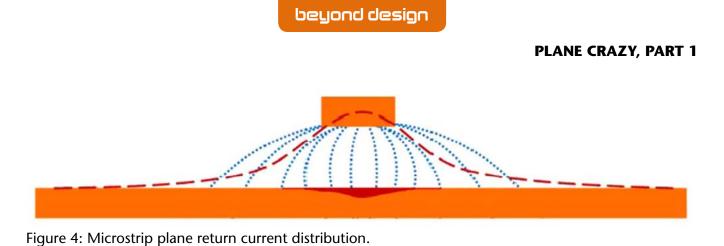

Figure 4 illustrates the cross-section on a microstrip (outer layer) trace and its associated plane return current distribution (red). Where the electric fields (blue) are more tightly coupled to the plane—directly below the trace—the return current also exhibits tighter coupling. But where the field spreads out from the trace, the larger loop area, between the signal and the return current path, increases the inductance. Return current tends to couple to the signal conductor and on the same side, of the plane nearest the signal, falling off in intensity, with the square of increased distance. A stripline (inner layer) return current distribution is narrower with the fields more intense above and below the trace.

Any voltage drop across a ground plane will excite cables terminating on the board, which causes them to radiate as dipole or monopole antennae. The amount of current needed to cause the radiation to exceed the FCC Class B emission requirements, in a one meter long antenna, is extremely small—in the vicinity of just a few  $\mu$ A. Therefore, even the smallest ground noise voltage is significant, since it only takes a few mV of potential to produce currents of this magnitude. Power and ground planes reduce the loop area and hence the inductance and the impedance, which in turn reduces the noise.

Although single-sided and double-sided boards have been used successfully in unshielded enclosures at frequencies of 20–25MHz, these cases are the exception rather than the rule. A design of this type, also requires a high level of EMC expertise and thus is time consuming and risky to produce. Above 10MHz, multilayer PCBs with at least two plane layers should be seriously considered.

Multilayer boards reduce radiated emissions by more than 10 db compared to a double-sided board—all other factors being equal. Embedding signals between the planes also reduces susceptibility to radiation, as well as providing ESD protection. So not only do we prevent noise from being radiated, but we also reduce the possibility of being affected by an external source.

The planes in a high-speed, digital board perform five crucial functions:

- 1. Allow the routing of controlled impedance transmission lines in both microstrip and stripline configurations.

- 2. Provide a reference voltage for the exchange of digital signals.

- 3. Distribute stable power to all logic devices.

- 4. Control crosstalk between switching signals.

- 5. Provide a shield for electromagnetic radiation on internal layers.

Next month, I will look at why solid power and ground planes encompass a distributed system of surprising complexity and how we can best use planar capacitance to reduce AC impedance of the PDN.

#### **Points to Remember:**

- Inductance may be reduced by minimizing the loop area enclosed by the current flow.

- Double-sided boards, using a power finger layout configuration, should be avoided as they create a large loop area for the return current.

beyond design

#### PLANE CRAZY, PART 1

- The power and ground grid configuration is the best approach for providing power delivery on double sided boards.

- Solid copper planes are a much better solution for high-speed design.

- At high speeds, return currents flow the path of least inductance which tends to direct the current directly below the signal trace.

- At high frequencies, a plane in a PCB is really two conductors, not one conductor, due to the skin effect.

- Any voltage drop across a ground plane will excite cables terminating on the board, which causes them to radiate as dipole or monopole antennae.

- Above 10MHz, multilayer PCBs with at least two plane layers should be seriously considered.

- Multilayer boards reduce radiated emission by more than 10 db compared to a double-sided board. **PCBDESIGN**

#### References

1. Barry Olney Beyond Design Columns: There are no One-Way Trips, The Dumping Ground, Losing a Bit of Memory, Stackup Planning 1-4.

2. Henry Ott, <u>Electromagnetic Compatibil-</u> <u>ity Engineering.</u>

3. Howard Johnson, <u>High-Speed Signal</u> <u>Propagation.</u>

4. Hashimoto & Nair, <u>Power Integrity for</u> <u>Nanoscale Integrated Systems.</u>

5. The ICD Stackup and PDN Planner, <u>www.</u> <u>icd.com.au.</u>

**Barry Olney** is managing director of In-Circuit Design Pty Ltd (ICD), Australia. This PCB design service bureau specializes in board-level simulation, and has developed

the ICD Stackup Planner and ICD PDN Planner software. To read past columns, or to contact Olney, <u>click here</u>.

### University of Twente Develops Versatile Method for Developing New Materials

Researchers at the University of Twente research institute MESA+ have devised an elegant method for fitting various functional coatings to silicon microwires. The research has been published today in the prestigious scientific journal Advanced Materials.

Microwires made of the semi-conductor silicon are used in numerous fields. It is generally necessary to 'functionalize' them, by adding a lay-

er of metal or a layer of a catalyst. In most cases, the wires are given a single layer, but in specific instances it is useful to put a different material on the bottom and on the top of the wires. However, creating these wires proved very dif-

ficult and the process of making them involved many steps. Researchers from the University of Twente have now developed a new method that makes creating wires of this kind easy. According to University of Twente Professor Jurriaan Huskens, this has provided chemists with a versatile method for creating new materials.

In their experiments, the University of Twente researchers first made microwires with a PN junction halfway along the wires. In the experiment, the wires were submerged into a solution containing platinum in the dark, causing the 'P side' of the wire to be covered in platinum. In the next stage, silver was added to the other side in the

> light. The result was a microwire with silver on the top and platinum on the bottom. The wires can be very valuable for the purpose of generating energy from sunlight or purifying water with the help of sunlight.

## lf you can dream it, we can help you build it.

ondon

Sun, July 8 Your City

刀 🖤 🗱

? ? ?

と回軍回殺

FAST

*IERCONNECT*

IDEAS BROUGHT TO LIFE

We provide all the services needed to take your idea into production:

- Board Design

- Product Development

- Embedded Software

- IOT Solutions

- FPGA Design

- Test Engineering