### Mistakes even the best engineers make How & why to build better libraries

Natasha Baker, Founder & CEO

**Overview** Why libraries matter Common symbol & footprint errors The need for verification Tools that can help

### In today's talk, you'll learn:

- 1. Why high-quality libraries matter

- 2. Common mistakes among a) the newbies and b) the pros

- 3. Tips & tricks to stay focused on building the best electronics possible!

- 12 years working on PCB design tools and libraries

- Electrical & computer engineer from the University of Toronto

- Founder of SnapEDA, electronics

library used by 1M engineers

## Why Libraries Matter

#### What is the scope of today's talk?

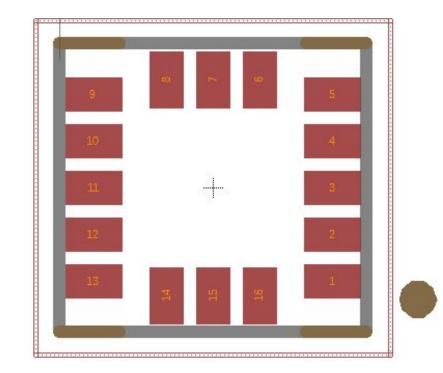

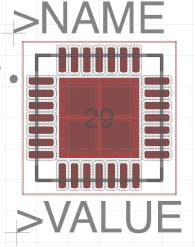

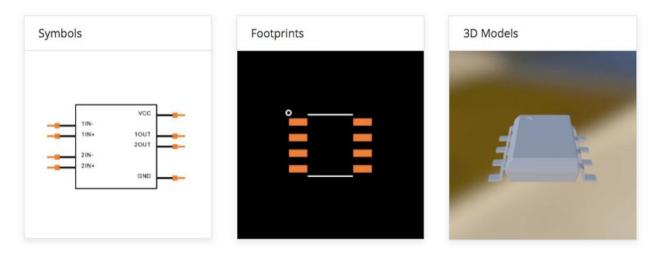

#### **PCB** Layout

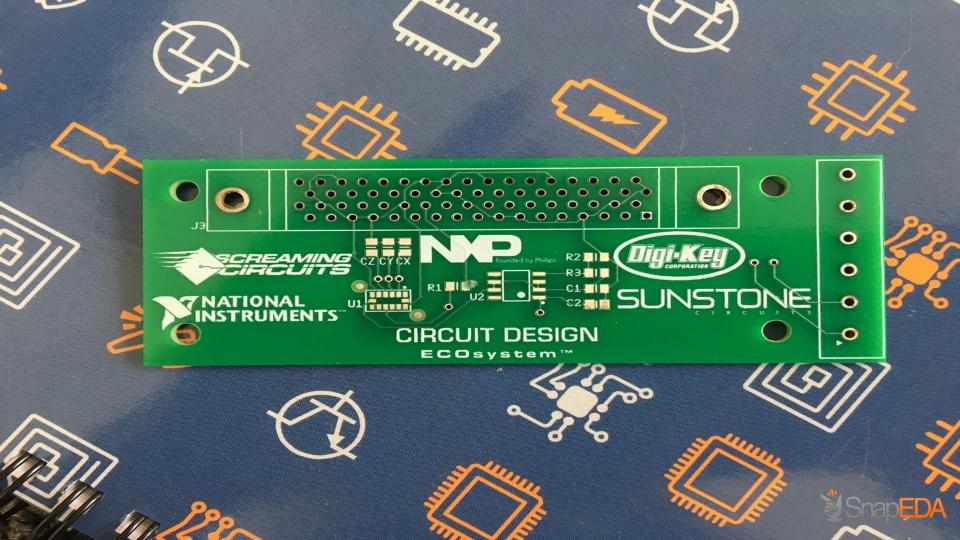

The **footprint** is used when designing the physical layout of the circuit board. It describes where the component will get soldered onto the board

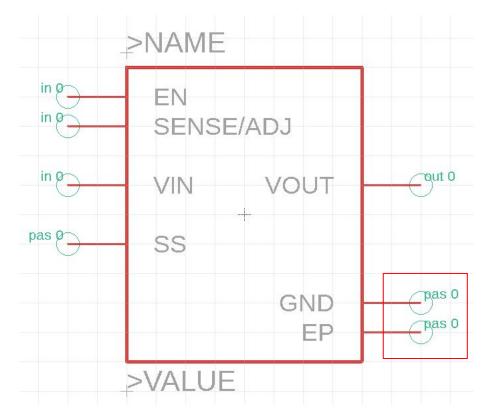

#### **Schematic Capture & Simulation**

Each component requires a **schematic symbol** which describes the pin functions and types. Engineers may also simulate their designs.

#### **Mechanical Design**

To see if a PCB will fit within the casing, **3D models** are used to check for clearances, and other factors.

#### Why well-defined libraries matter

Necessary for ensuring proper manufacturing

To enable other CAD tool features to function properly (ex: ERC)

Documentation (ensure readability and re-use through consistency)

### Why are libraries so hard to get right?

Extremely detail-oriented

- Lack of datasheet consistency and standards

- Lack of industry standards or alignment

Varying manufacturing capabilities

Lack of universal file format

#### **Standards**

#### The scope is massive

Many details required for each pin, pad and part

Changing industry standards

Company-specific standards

300 Million+ Electronics Components Infinite user preferences

Application-specific requirements

Tool-specific quirks

### "Never discuss politics, religion or PCB library standards in polite company."

### Library Errors -The Basics

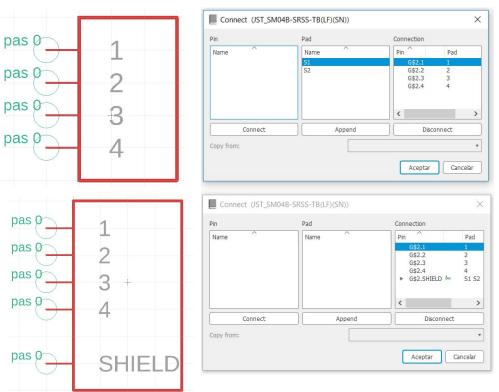

# # 1 Pin mapping issues

Mapping pins to the wrong pads is a critical mistake, causing improperly connected pins, or even worse, creating shorts.

**How to avoid:** Double check all connections.

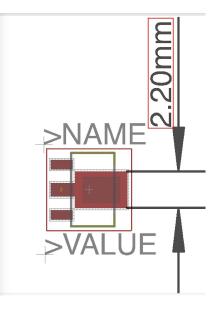

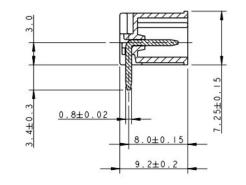

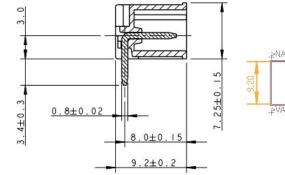

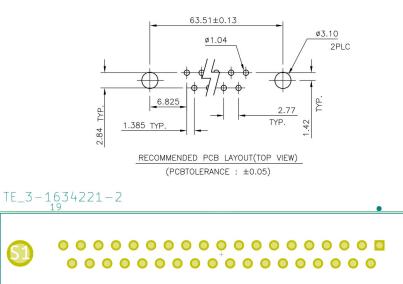

### #2 Pad dimension errors

wing pad layouts, kes.  $\frac{1}{y} = \frac{1}{y} = \frac{1}{y}$

Suggested Pad Layout (Cont.)

| Dimensions | Z           | X           | X1          | X2          | Y           | Y1          | E           |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|            | (mm)/(inch) |

| Value      | 4.600/0.181 | 0.550/0.022 | 1.850/0.073 | 0.800/0.031 | 1.300/0.051 | 1.475/0.058 | 1.500/0.059 |

AP2204

Z

If you are manually drawing pad layouts, it is easy to make mistakes.

If you get one pad length off by a fraction of a millimeter it can cause soldering issues.

# #3 Rounding dimensions

During conversion of metric to imperial units or vice versa, units should never be rounded

#### #4 Silkscreen too close to pads

One of the most common issues seen in library design is silkscreen overlapping exposed copper on pads.

If this happens it could inhibit the solder from flowing and will result in a bad joint.

# #4 Wrong outline dimensions

Wrong component outline and courtyard dimensions will cause overlapping of nearby components in the PCB and could produce critical manufacturing issues.

Confusing component outline dimensions may result in trying to fit a RA header on a vertical header footprint, or vice versa.

#### #5 Wrong pin sequence

Some connectors are numbered from top to bottom, others are numbered from left to right. If the pin numbering of your footprint is incorrect you'll have wrong connections.

VAL\*\* 37

20

SZ

## Library Errors - The Ones Even Pros Miss

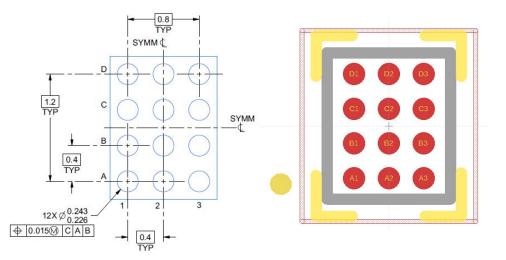

#### **#1 Mirrored views**

This occurs when the top view of a part is mistaken for the bottom view. Generally, component vendors draw based on the top view. But occasionally, they'll do the opposite.

#### #2 Wrong or misinterpreted datasheets

Learning to interpret datasheets and paying attention to the details is key. For senior engineers, many errors result from datasheet misinterpretations.

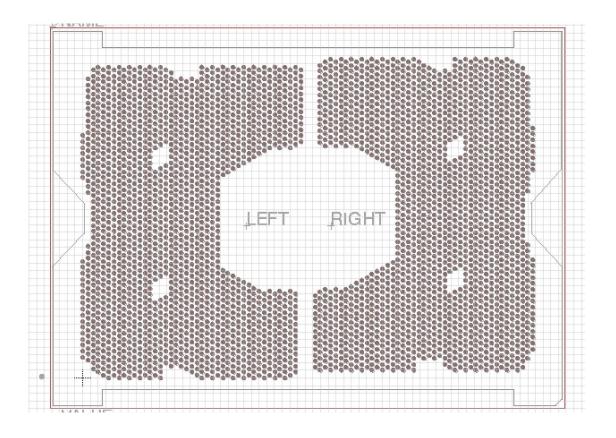

#### **#3 Wrong centroid**

The center-of-mass of a part is defined by an X-Y location and this concept is known as the part centroid.

If your centroid coordinates are off then the pick-and-place machine will try to pick components from a location that may not stick well to the package.

#### #4 Wrong component zero orientation

The zero component orientations expressed in IPC-7351 are defined for the description of electronic component orientations. They're important for the pick-and-place to figure out how to place the component during assembly

# #5 Improper pin definitions

To define the logical direction of signal flow in a schematic symbol, you need to understand the function of the component you are creating.

If pins are not defined properly ERC checks will not work .

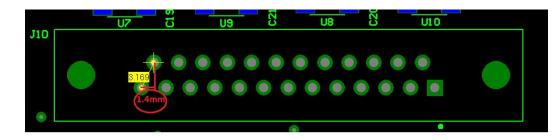

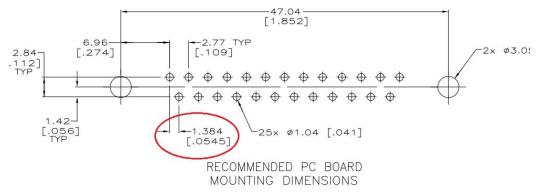

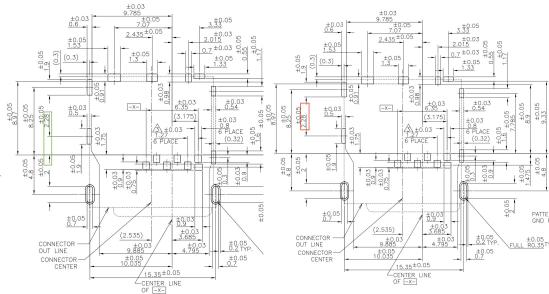

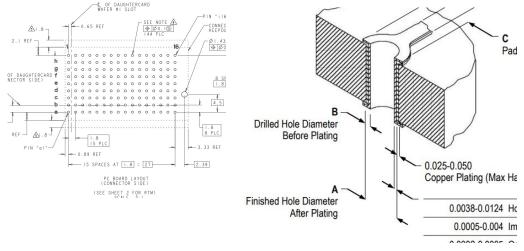

#### #6 Misinterpreting plated versus non-plated hole sizes

Accidentally overlooking this and choosing the wrong finished hole size, can cause holes to be too big.

Most manufacturers assume that the size you specify is the "finished hole size" (after plating).

| CONNECTOR                       | TIED | DIMENSION   |                    |      |

|---------------------------------|------|-------------|--------------------|------|

| CONNECTOR                       | TIER | A (Nominal) | В                  | C    |

| Vertical Receptacle (Backplane) | 1, 2 | 0.56 (Ref)  | 0.63-0.67          | 1.02 |

|                                 | 1    | 0.56 (Ref)  | 0.63-0.67          | 1.02 |

| Right-Angle Plug (Daughtercard) | 2    | 0.46 (Ref)  | 46 (Ref) 0.53-0.57 |      |

Figure 4

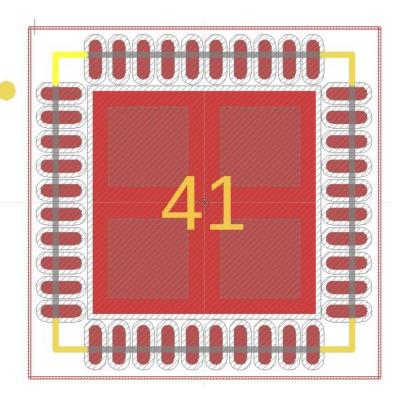

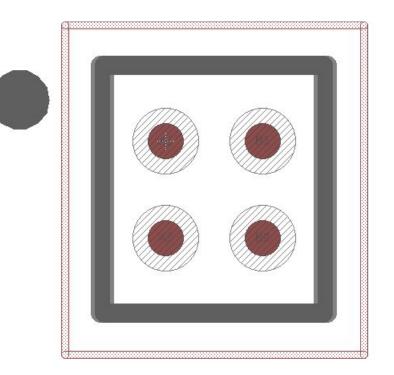

#### #7 Not breaking up solder paste in thermal pads

QFN mounted with too much solder in center pad area

This can cause float where the part is too high and doesn't connect to pins.

QFN mounted with reduced solder paste in center pad area

# Question: Do different assembly shops handle footprints differently?

# Question: Do different assembly houses require different footprints?

# Checklists & Verification

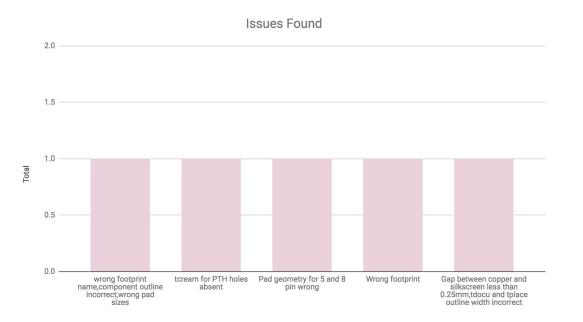

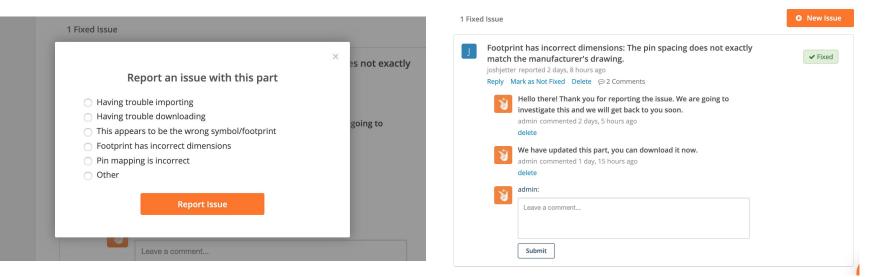

### The need to verify libraries

• Regardless of whether you got a library from the web, component vendor website, or made it yourself, it always needs to go through a thorough verification process

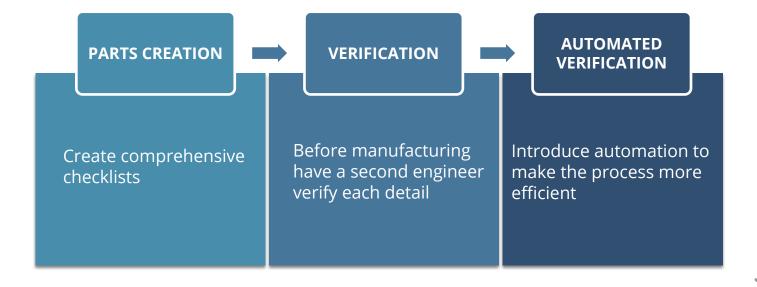

#### **Step 1: Define the process**

#### Step 2: Create, maintain and enforce checklists

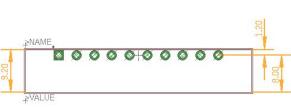

Package name should follow IPC naming convention

Follow IPC Zero orientation with pin 1 upper left

Ensure that the pin mapping is the top view of the chip and not a mirrored view from the bottom.

Ensure the spacing between silkscreen and copper is at least 0.25mm + 0.0635 (line width / 2) = 0.32

Body outlines or any part of the footprint created with the tPlace layer should not collide/overlap with the pads.

Add a body outline (0.127 mm lead width) in tDocu and tPlace layer

Exposed pad's tCream layer (paste) should be 40%-50% of the area of the exposed pad

Add a tKeepout outline with 0.05mm lead width enclosing the footprint (0.25mm away from the pads/component outline)

Irregular-shapes pads (including tcream, tstop, tkeepout) created with polygon tool, lead width should be 0.001 mm (not zero)

For components with cut-outs, draw the cut-out in Milling layer using line width 0 mm

#### Step 3: Measure, learn & iterate

#### **Step 4: Automate**

- To prevent human error, and minimize library efforts, automation is your friend!

- What parts of the creation and verification processes can you automate?

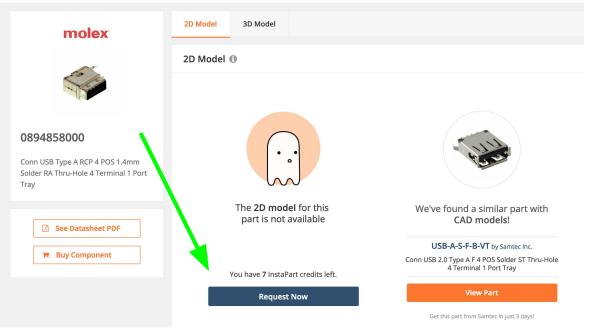

## What tools are available to help?

• Symbols, footprints, and 3D models for millions of electronics components

EAGLE

cādence OrCAD Altum

Mentor

A Siemens Business

Cad

Design Software

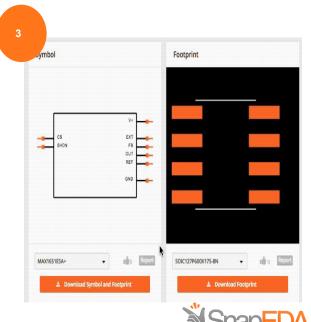

#### **#InstaBuild**

• Create schematic symbols using simple computer vision and OCR in minutes

| PIN | NAME |                                                                                                                                        |  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | OUT  | Sense Input for fixed 5V or 3.3V output operatio<br>Although it is connected to the output of the circ<br>adjustable-output operation. |  |

| 2   | FB   | Feedback Input. Connect to GND for fixed-outp<br>GND for adjustable-output operation. See Setti                                        |  |

| 3   | SHDN | Active-High Shutdown Input. Part is placed in a<br>ence, output, and external MOSFET are turned                                        |  |

| 4   | REF  | 1.5V Reference Output that can source 100µA.                                                                                           |  |

| 5   | V+   | Positive Power-Supply Input                                                                                                            |  |

| 6   | CS   | Current-Sense Input. Connect current-sense<br>equals the current-limit trip level, the external                                        |  |

| 7   | EXT  | Gate Drive for External P-Channel MOSFET. EX                                                                                           |  |

| 8   | GND  | Ground                                                                                                                                 |  |

|   | Remove    | Remove    |        |

|---|-----------|-----------|--------|

|   | Pin Names | Pin Types |        |

| X | 1         | OUT       | Auto 🗸 |

| X | 2         | FB        | Auto 🗸 |

| X | 3         | SHDN      | Auto 🗸 |

| X | 4         | REF       | Auto 🗸 |

| X | 5         | V+        | Auto 🗸 |

| X | 6         | CS        | Auto 🗸 |

| X | 7         | EXT       | Auto 🗸 |

| X | 8         | GND       | Ŧ. )   |

• Request any symbol & footprint and get it in 24h

• Validate libraries in real-time

#### Verification Checker Beta 🕄

This report for the MT46V32M16BN-5B:F was generated by our patent-pending Verification Checker. It checks for common manufacturability issues to ensure quality.

Legend: 🖌 Pass ! Please Inspect 🗶 Fail

| ~  | Manufacturability                                                          | Checks that identify issues related to manufacturability         |  |  |  |

|----|----------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| ~  | Silkscreen object should not overlap pads                                  |                                                                  |  |  |  |

| ~  | Footprint (FBGA60-8X20) should be centered at (0, 0) and is at (0, 0)      |                                                                  |  |  |  |

| ~  | Surface mount pads should be or                                            | n the top layer                                                  |  |  |  |

| ~  | Documentation                                                              | Ensuring that schematic and board layout have good documentation |  |  |  |

| ~  | Package FBGA60-8X20 should have                                            | ve the text 'NAME' for the layer name text.                      |  |  |  |

| ~  | Package FBGA60-8X20 should have the text 'VALUE' for the layer value text. |                                                                  |  |  |  |

| ~  | Text should be on the documenta                                            | ation layer                                                      |  |  |  |

| i) | Miscellaneous                                                              | Miscellaneous checks                                             |  |  |  |

| 1  | Package name FBGA60-8X20 show                                              | uld be an IPC name                                               |  |  |  |

|    |                                                                            |                                                                  |  |  |  |

#### • Share and learn from the engineering community

## Summary

#### Summary

Libraries are necessary for reliable manufacturing, readability, and ERC

Implementing verification checklists and processes is essential

Other tools can help increase the efficiency and productivity

#### Thanks to SnapEDA's Component Engineering Team!

## Questions?

natasha@snapeda.com